【導讀】本文詳細解說了I2C的概念,對I2C總線概述進行了概述,并且從I2C總線時序出發,對其進行總結。最后詳細描述了I2C總線時序的工作過程。相信讀者閱讀本文后,會對I2C總線及時序更加了解。

一.概述:

I2C 是Inter-Integrated Circuit的縮寫,發音為"eye-squared cee" or "eye-two-cee" , 它是一種兩線接口。

I2C 只是用兩條雙向的線,一條 Serial Data Line (SDA) ,另一條Serial Clock (SCL)。

SCL:上升沿將數據輸入到每個EEPROM器件中;下降沿驅動EEPROM器件輸出數據。(邊沿觸發)

SDA:雙向數據線,為OD門,與其它任意數量的OD與OC門成"線與"關系。

二.輸出級

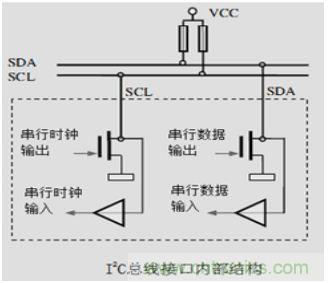

圖1

1)由于SDA、SCL為漏極開路結構(OD),因此它們必須接有上拉電阻,阻值的大小常為 1k8, 4k7 and 10k ,但1k8 時性能最好;當總線空閑時,兩根線均為高電平。連到總線上的任一器件輸出的低電平,都將使總線的信號變低,即各器件的SDA及SCL都是線"與"關系。

2)引腳在輸出信號的同時還將引腳上的電平進行檢測,檢測是否與剛才輸出一致,為"時鐘同步"和"總線仲裁"提供了硬件基礎。

三. 主設備與從設備

系統中的所有外圍器件都具有一個7位的"從器件專用地址碼",其中高4位為器件類型,由生產廠家制定,低3位為器件引腳定義地址,由使用者定義。主控器件通過地址碼建立多機通信的機制,因此I2C總線省去了外圍器件的片選線,這樣無論總線上掛接多少個器件,其系統仍然為簡約的二線結構。終端掛載在總線上,有主端和從端之分,主端必須是帶有CPU的邏輯模塊,在同一總線上同一時刻使能有一個主端,可以有多個從端,從端的數量受地址空間和總線的最大電容 400pF的限制。

● 主端主要用來驅動SCL line;

● 從設備對主設備產生響應;

二者都可以傳輸數據,但是從設備不能發起傳輸,且傳輸是受到主設備控制的。

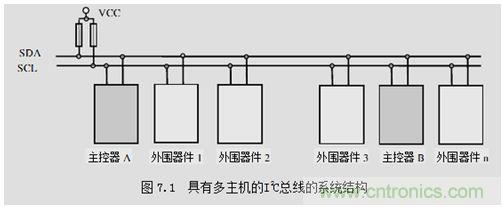

圖2

● 普通模式:100kHz;

● 快速模式:400kHz;

● 高速模式:3.4MHz;

沒有任何必要使用高速SCL,將SCL保持在100k或以下,然后忘了它吧。

[page]

五.時序:

1、協議

(1)空閑狀態

I2C總線的SDA和SCL兩條信號線同時處于高電平時,規定為總線的空閑狀態。此時各個器件的輸出級場效應管均處在截止狀態,即釋放總線,由兩條信號線各自的上拉電阻把電平拉高。

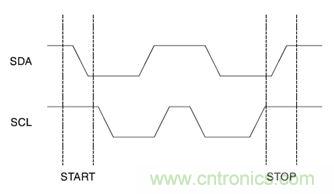

(2)起始位與停止位的定義:

起始信號:當SCL為高期間,SDA由高到低的跳變;啟動信號是一種電平跳變時序信號,而不是一個電平信號。

停止信號:當SCL為高期間,SDA由低到高的跳變;停止信號也是一種電平跳變時序信號,而不是一個電平信號。

圖3

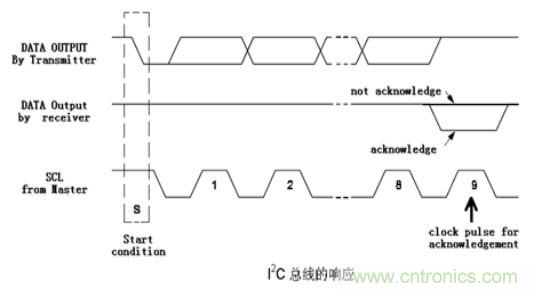

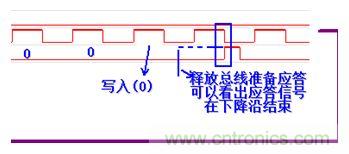

發送器每發送一個字節,就在時鐘脈沖9期間釋放數據線,由接收器反饋一個應答信號。 應答信號為低電平時,規定為有效應答位(ACK簡稱應答位),表示接收器已經成功地接收了該字節;應答信號為高電平時,規定為非應答位(NACK),一般表示接收器接收該字節沒有成功。 對于反饋有效應答位ACK的要求是,接收器在第9個時鐘脈沖之前的低電平期間將SDA線拉低,并且確保在該時鐘的高電平期間為穩定的低電平。 如果接收器是主控器,則在它收到最后一個字節后,發送一個NACK信號,以通知被控發送器結束數據發送,并釋放SDA線,以便主控接收器發送一個停止信號P。

圖4

這里面給我們的兩個信息是:1)接收器在SCL的上升沿到來之前的低電平期間拉低SDA;2)應答信號一直保持到SCL的下降沿結束;正如前文紅色標識所指出的那樣。

圖5

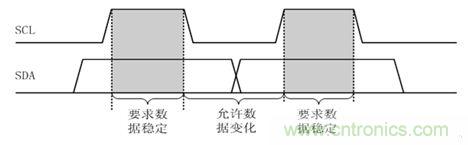

I2C總線進行數據傳送時,時鐘信號為高電平期間,數據線上的數據必須保持穩定,只有在時鐘線上的信號為低電平期間,數據線上的高電平或低電平狀態才允許變化。

我的理解:雖然只要求在高電平期間保持穩定,但是要有一個提前量,也就是數據在SCL的上升沿到來之前就需準備好,因為在前面I2C總線之(一)---概述一文中已經指出,數據是在SCL的上升沿打入到器件(EEPROM)中的。

圖6

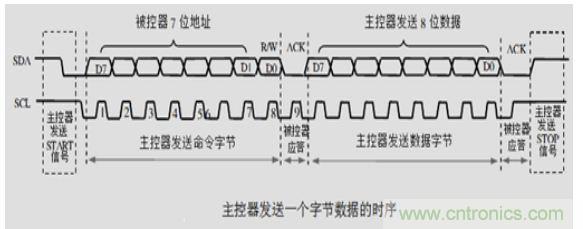

在I2C總線上傳送的每一位數據都有一個時鐘脈沖相對應(或同步控制),即在SCL串行時鐘的配合下,在SDA上逐位地串行傳送每一位數據。數據位的傳輸是邊沿觸發。

[page]

2、工作過程

總線上的所有通信都是由主控器引發的。在一次通信中,主控器與被控器總是在扮演著兩種不同的角色。

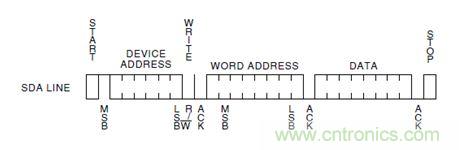

(1)主設備向從設備發送數據

主設備發送起始位,這會通知總線上的所有設備傳輸開始了,接下來主機發送設備地址,與這一地址匹配的slave將繼續這一傳輸過程,而其它slave將會忽略接下來的傳輸并等待下一次傳輸的開始。主設備尋址到從設備后,發送它所要讀取或寫入的從設備的內部寄存器地址; 之后,發送數據。數據發送完畢后,發送停止位:

寫入過程如下:

發送起始位

● 發送從設備的地址和讀/寫選擇位;釋放總線,等到EEPROM拉低總線進行應答;如果EEPROM接收成功,則進行應答;若沒有握手成功或者發送的數據錯誤時EEPROM不產生應答,此時要求重發或者終止。

● 發送想要寫入的內部寄存器地址;EEPROM對其發出應答;

● 發送數據

● 發送停止位.

● EEPROM收到停止信號后,進入到一個內部的寫入周期,大概需要10ms,此間任何操作都不會被EEPROM響應;

圖7

圖8

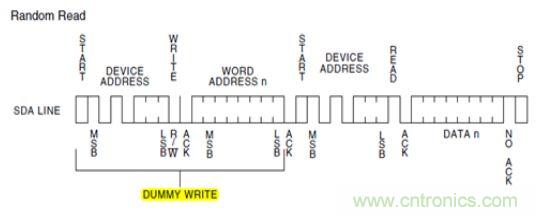

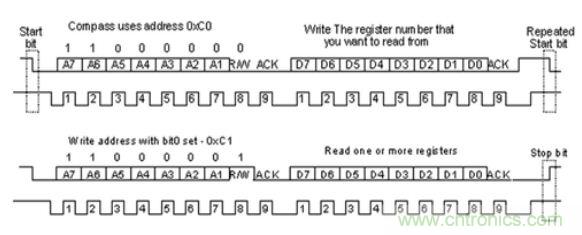

(2)主控器讀取數據的過程:

讀的過程比較復雜,在從slave讀出數據前,你必須先要告訴它哪個內部寄存器是你想要讀取的,因此必須先對其進行寫入(dummy write):

● 發送起始位;

● 發送slave地址+write bit set;

● 發送內部寄存器地址;

● 重新發送起始位,即restart;

● 重新發送slave地址+read bit set;

● 讀取數據

主機接收器在接收到最后一個字節后,也不會發出ACK信號。于是,從機發送器釋放SDA線,以允許主機發出P信號結束傳輸。

● 發送停止位

圖9

圖10