【導讀】求助啊!請教下有經驗的各位,這個數據總線上的波形到底應該是什么樣的,我這個板子上第二條數據總線上掛著4個芯片,分別是一個SRAM,雙口ram,一塊FPGA和一塊DSP,到底是什么問題導致數據總線出問題。

先簡單介紹一下電路板,上面有兩條數據總線,分別用兩個DSP控制,兩個DSP通過雙口RAM通信。一條總線上掛著FPGA,一條掛著一個CPLD。

說說問題,就是發現用DSP給FPGA寫數,然后發到測試點看波形,發現本來寫0的數有的時候會讀成1。

開始以為是FPGA程序使用inout的口沒有釋放總線,就把FPGA的數據線配置成了輸入,相當于只能寫不能讀,仍然存在寫錯數的情況,而且沒有什么規律。

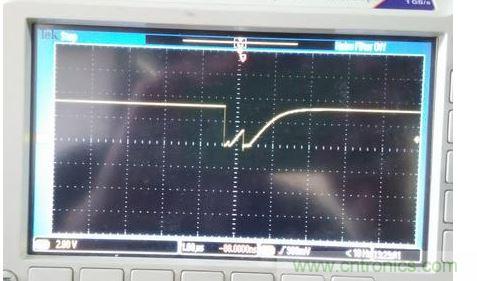

于是測量數據總線。有下面的圖。這里的程序是寫一次數再讀一次數。感覺這個明顯不對勁。

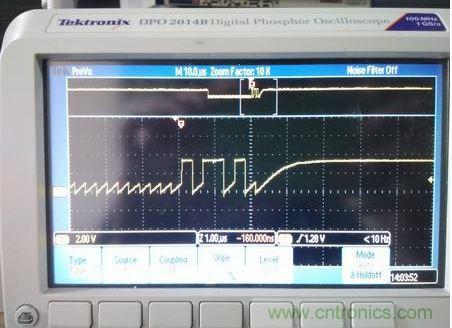

后來又把FPGA沒有加載程序,單從雙口RAM里讀數據。有下面的波形。

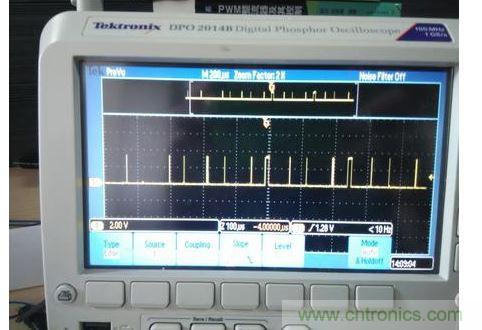

看起來好像跟FPGA沒有什么關系。后來我又測量了另外一條總線的波形如下圖

這個看起來就比較正常。后來我懷疑是不是哪個芯片自帶上拉電阻,又把FPGA的輸出口配置上了下拉電阻有下面的波形。

感覺像是DSP的IO口出了問題,因為這個板子上FPGA剛換上新的。

我記得只有一次不當使用,就是之前程序有句話寫錯了,只要不讀寫FPGA,FPGA就會把所有數據線拉低。不知道這樣會不會由于FPGA的驅動能力過強,將DSP的IO口燒壞。

所以請教下有經驗的各位,這個數據總線上的波形到底應該是什么樣的,我這個板子上第二條數據總線上掛著4個芯片,分別是一個SRAM,雙口ram,一塊FPGA和一塊DSP,到底是什么問題導致數據總線出問題。

還有一點就是,在這個板子上,就是通過數據線把這四個芯片連了起來,數據線上沒有任何串入的電阻和并入的電容,希望各位大蝦幫幫忙,困擾了挺久的時間了。