【導讀】在電子系統中,用于連接電路板和各個模塊之間的連接器不僅價格昂貴而且占據了電路板和系統的寶貴空間,并且它們還會降低產品的穩定性。

在電子系統中,用于連接電路板和各個模塊之間的連接器不僅價格昂貴而且占據了電路板和系統的寶貴空間,并且它們還會降低產品的穩定性。

萊迪思開發了一種創新的方法,讓系統架構師和開發人員使用尺寸極小的低功耗FPGA來大幅度減少板間和模塊間的連接器數量,在增加系統穩定性的同時,降低了空間占用和成本。

擁有FPGA設計經驗的開發者還能自定義該解決方案。即便沒有FPGA設計經驗,開發人員依然能夠輕松快速完成部署。

優化連接

當今的絕大多數電子系統都包含兩個及以上的電路板和/或模塊。(除非另有說明,否則下文中的術語“電路板”或“板”將默認包括“模塊”。)

對于系統設計師而言,經常面臨的問題就是連接電路板進行數據傳輸。常見的解決方案是將多引腳連接器安裝在電路板上,然后使用多個線束或導線將電路板連接在一起。

然而,每個連接器的引腳都是潛在的故障點,因此,除了增加成本和占用空間外,連接器通常還是影響 電子系統可靠性的關鍵因素。這意味著最大程度減少板間連接可以降低成本、減小空間占用并提高系統穩定性。

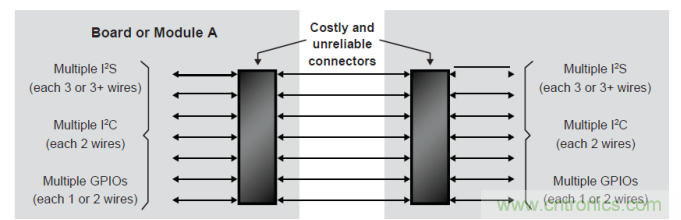

如圖1所示,這些電路板之間信號的通信速率相對較低,使用的是通用I/O(GPIO)或者I2C和I2S等串行接口。

圖1. 傳統的連接器不僅價格高、占用空間,而且會降低系統穩定性

各種系統的設計人員——從手持設備、筆記本電腦到工業控制器——都迫切希望最大程度減少連接器引腳數量和電路板之間的連線。

單線聚合:FPGA的優勢

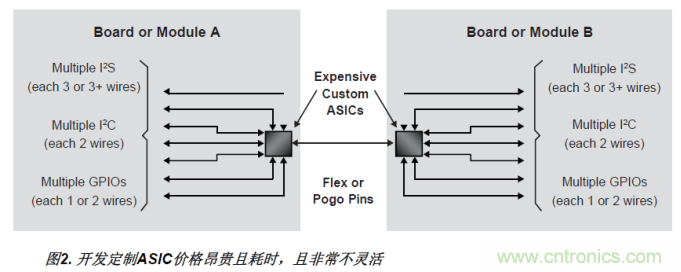

單線聚合(SWA)背后的原理是將多個信號匯聚到一個時分復用(TDM)信號中,而該信號在電路板間傳輸僅需要一根線纜。實現該方案的一個做法是為每種產品創建定制的專用集成電路(ASIC)(圖2)。

然而,定制ASIC的解決方案有許多缺點,如開發成本高昂且耗時。更糟的是,它們所包含的任何算法和功能實際上都是“凍結在芯片中”,這意味著它們無法適應不斷變化的需求。例如銷售主管突然宣布:“我們最大的客戶說需要用兩個I2C通道替代其中一個I2S接口。”

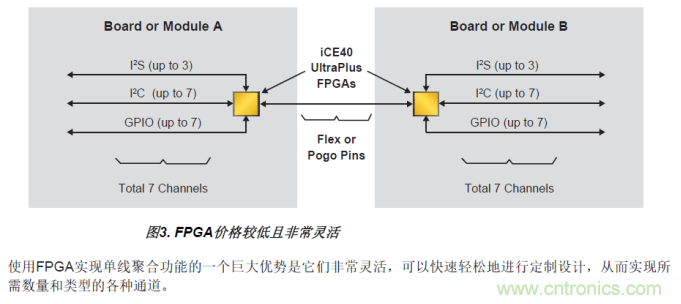

理想的解決方案是采用低成本的現場可編程門陣列(FPGA),如萊迪思半導體的iCE40 UltraPlus™器件(圖3)。

FPGA設計人員使用iCE40 UltraPlus實現單線聚合

上一段中有這樣一句表述: “基于FPGA的單線聚合可以快速輕松地進行定制設計”。這句話有個前提那就是需要非常熟悉FPGA設計。

如果您是FPGA設計人員,萊迪思可為您提供行業最易于使用的FPGA開發工具。此外,在單線聚合解決方案中,萊迪思還提供全套參考設計資源,搭配其行業領先的iCE40 UltraPlus™ FPGA:

• 易于修改、參數化的單線聚合參考設計的源代碼,可在萊迪思Radiant設計工具上運行

• 免費使用Lattice Radiant®設計工具

• 相關的參考設計用戶指南

• 單線聚合演示和開發板

然而,并非所有的設計團隊都有FPGA設計經驗。幸好,萊迪思也專為非FPGA設計人員提供解決方案。

非FPGA設計人員使用iCE40 UltraPlus實現單線聚合

拿一個基于微控制器(MCU)的系統舉例。設計團隊的某些成員可以熟練使用C或C ++之類的語言來開發軟件,然后運行軟件編譯器,軟件編譯器以機器代碼生成可執行文件。團隊的其他成員只需將此機器代碼文件加載到MCU中,無須了解編程相關的任何信息。

同樣,FPGA開發人員的專長是使用Verilog或VHDL等硬件描述語言(HDL) 描述設計,然后運行被稱之為邏輯綜合引擎的硬件編譯器,將HDL生成配置文件,也就是常說的位流。團隊的其他成員可以將位流載入FPGA,無需了解關于FPGA設計的任何內容。

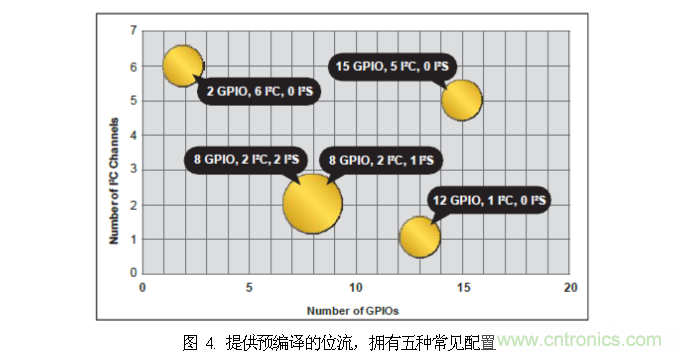

首個針對非FPGA設計人員的單線聚合解決方案提供了五種預先綜合的位流(圖4)。這些配置是對諸多實際應用分析的結果,可以滿足各類系統設計的要求。

用戶可以從萊迪思網站單線聚合解決方案(latticesemi.com/zh-CN/singlewire)下載《關于位流文件的用戶指南》。指南描述了如何將預配置的位流加載到iCE40 UltraPlus FPGA中。

此外,萊迪思還提供免費的單線聚合設計服務。您可以訪問萊迪思的單線聚合開發板網頁(latticesemi.com/zh-CN/products/developmentboardsandkits/singlewire),填寫表格,明確您的設計所需的通道組合,之后萊迪思設計團隊將通過電子郵件給您發送相應的位流文件。

iCE40 UltraPlus FPGA

為了更好地闡述本文內容,我們需要簡單了解一下實現單線聚合的器件。iCE40 UltraPlus FPGA擁有靈活的邏輯架構、2800或5280個4輸入查找表(LUT)、可定制的通用I/O(GPIO)、多達80 Kb的嵌入式存儲塊(EBM)和多達1 Mb嵌入式SRAM。

iCE40 UltraPlus FPGA可以在大多數應用中實現超低功耗的高級處理功能,其靜態電流低至75 uA,工作電流低至1-10 mA。此外iCE40 UltraPlus FPGA還提供多種封裝選項,滿足各類應用的需求:2.15 x 2.50 mm超小尺寸WLCSP封裝專為消費電子和物聯網設備優化,0.5 mm引腳間距的7 x 7 mm QFN封裝則可以滿足成本優化型應用的需求。

由于配置位流可以直接加載到基于SRAM的配置單元中,因此iCE40 UltraPlus FPGA可以反復地重新編程。這樣設計人員可嘗試使用不同的設計和位流,是項目原型開發階段的最佳選擇。

如果在產品中使用基于SRAM的iCE40 UltraPlus器件,那么可以通過板上MCU或從外部SPI閃存設備來加載配置。

另外,iCE40 UltraPlus FPGA還包含一次性可編程(OTP)片上非易失性配置存儲器(NVCM),非常適合大規模量產。對NVCM進行編程后,器件將自動、快速且安全地從該配置啟動。

單線聚合演示和開發板

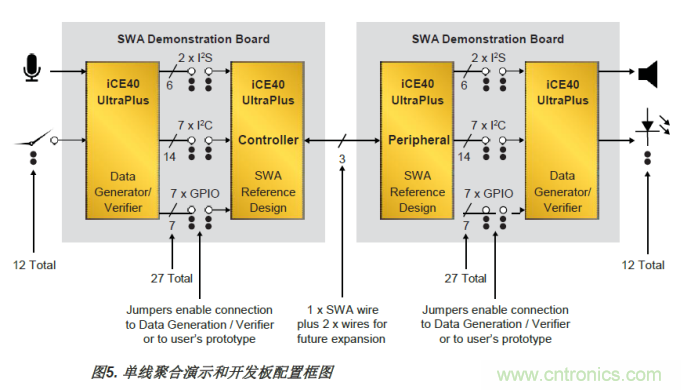

SWA演示和開發板包含兩片iCE40 UltraPlus FPGA。一片用作數據生成器或數據驗證器,另一片用于實現單線聚合參考設計(用作控制器或外設)。

圖5展示了兩塊開發板的典型使用場景。在此案例中,左邊的開發板包括了數據生成器和單線聚合控制器,右邊的開發板則包括了單線聚合的外設和數據驗證器。

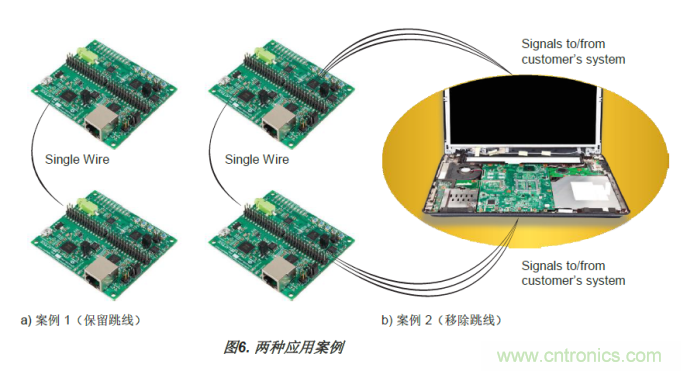

觀察圖中的跳線。如果保留這些跳線,則來自左側演示板上數據發生器的數據將被饋送到單線聚合控制器參考設計中,該參考設計將其聚合為單個信號傳輸至右側板上。右側演示板上的單線聚合外設參考設計將接收聚合的信號,并將解聚的信號饋送到數據驗證器。下圖6(a)展示了這一過程。

單線聚合解決方案特性總結

如上所述,單線聚合參考設計在兩片iCE40 UltraPlus FPGA上運行,其中一個FPGA以時分復用方式聚合多個數據流(例如I2C、I2S和GPIO),然后通過單線將其發送到另一個FPGA,解聚回原來的數據流。

兩片FPGA之間的單線通信速度約為7.5 Mbps。該設計也可自行配置——可以調整I2C / I2S總線數量和GPIO數量以及單線協議數據包的長度,并且FPGA之間的單線協議擁有錯誤檢測和重試功能。該解決方案的特性的簡要概述如下:

• 最多聚合7個通道

• 單線上的原始數據速率約為7.5 Mbps或更高

• 數據包長度可變,可有效利用單線帶寬

• 接收端出現奇偶校檢錯誤時可重新進行傳輸

• 支持I2C的Fast-mode (400 kbps)和Fast-mode Plus(1 Mbps)

• I2C中斷可以使用GPIO和基于事件的傳輸來實現

• I2S支持單個立體聲通道、48K hz采樣速率、高達32位采樣以及雙向支持

小結

當今的許多電子系統都包括多塊電路板。此外,這些系統大多使用多種不同類型接口(例如I2C、I2S和GPIO)從外圍設備和傳感器收集數據,并在電路板之間傳輸。

在擁擠的電路板和連接器上傳輸信號本身可能會帶來很多問題,除此之外,電路板的面積和系統內部空間通常十分寶貴。除了增加成本和占用空間外,連接器通常還是系統中最不可靠的組件。

萊迪思開發了一種創新的方法讓系統架構師和開發人員使用小尺寸、低成本的FPGA來實現單線聚合,顯著減少板間連接器的數量,在提高系統穩定性的同時還減小了系統尺寸和成本。

擁有FPGA設計經驗的開發人員可以自定義該解決方案。此外,即便沒有任何FPGA開發經驗,開發人員也能快速輕松地完成部署。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請電話或者郵箱聯系小編進行侵刪。