【導讀】傳統的AC-PDP電源一般采用兩級方案,即PFC級+DC/DC變換的電路拓撲結構。它們分別有各自的開關器件和控制電路。盡管其能夠獲得很好的性能,但其體積過大,成本太高,電路比較復雜。因此,對其進行小型化改造也成了AC-PDP技術研究的一個方向。

由于AC-PDP驅動控制電路的復雜性,導致了其開關電源的復雜性。分析可知,不管從傳輸能量角度還是從所占體積的角度,PFC模塊和掃描驅動電極DC/DC變換模塊都占有相當大的比例。因此,對這兩部分的改造就成為AC-PDP開關電源小型化改造的一個切入點。本文根據單級功率因數校正的工作原理,提出了一種AC-PDP電極驅動電源模塊改進方案。

單級PFC維持電極電源模塊的拓撲結構及工作原理

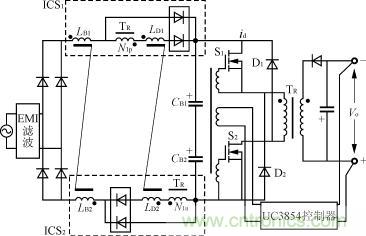

本文采用的單級功率因數校正變換器電路拓撲結構如圖1所示。單相交流電經全波整流后,通過串聯兩個感性ICS(Input-current shaping)接到雙管反激的DC/DC變換單元。

圖1:主電路拓撲結構

圖中的兩個ICS單元完全相同,即LB1=LB2,LD1=LD2,N1p=N1n。采用這種雙ICS的單元結構是為了減小儲能電容器上的電壓以及流過開關管的電流。

下面通過開關管的動作過程分析整個電路的工作原理以及工作過程。

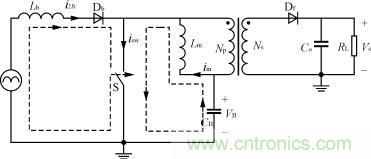

1)S1和S2導通期間

其簡化電路如圖2(a)所示。開關管導通,儲能電容經圖2(a)中右邊回路釋放電能,反激變換器TR開始儲能,iDC由零開始上升。線圈N1p及N1n分別感應產生左負右正和左正右負的電壓,D1n和D1p開始導通,D2n和D2p截止。Vin經圖2(a)中左邊的回路給儲能電容CB1及CB2充電,iin開始上升,電感LB1,LB2,LD1,LD2充電。

(a)開關管導通時的電路圖

(b)開關管截止時的電路圖

圖2:開關管通斷時的簡化電路

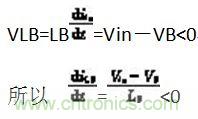

因為VLB1=VLB2,VLD1=VLD2,為了分析方便,令

VLB=VLB1+VLB2=2VLB1VLD=VLD1+VLD2=2VLD1

在右邊的回路中,根據基爾霍夫定律有

式中:Vin為全波整流后的輸出電壓,即Vin=Vs|sinωt|;

VB=VB1+VB2;

N1為繞組N1n及N1p的匝數;

Np為反激變換器原邊主繞組的匝數。

又因為

2)S1和S2截止期間

簡化電路圖如圖2(b)所示。此時iDC等于零,反激變換器給負載供電。線圈N1P及N1n分別感應產生左正右負和左負右正的電壓,D1n及D1p反向截止,D2n及D2p續流導通。根據基爾霍夫定律有

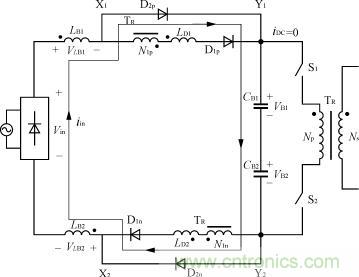

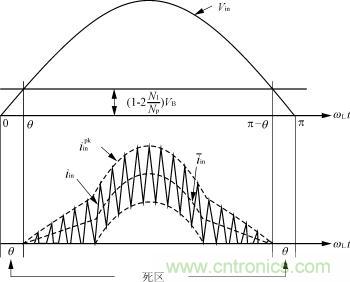

從上面的分析可知,當gongshi4時,D1n,D1p,D2n,D2p全部截止,電流iin為零,電感LB1及LB2中沒有電流流過,即回路電流iin存在一個死區θ(dead angle),是不連續的。也就是說,在半個工頻周期內,只有一部分時間電感LB的電流連續工作,iLB在半個工頻周期內的波形如圖3所示。

由圖3可以看出,當輸入電壓為交流正弦波時,其輸入電流為一含有高頻紋波的近似正弦波。兩者相位基本相同,提高了輸入端的功率因數。

圖3:輸入電壓電流波形圖

試驗結果

根據4電極42英寸(107cm)彩色PDP驅動電路的要求,設計驅動電源模塊的參數為:

輸入電壓 AC170~250V;

輸出電壓 DC200~240V;

輸出電流 1A。

實驗電路采用UC3845作為開關管的控制芯片,開關的工作頻率為80kHz。DC/DC變換部分采用雙管反激電路。

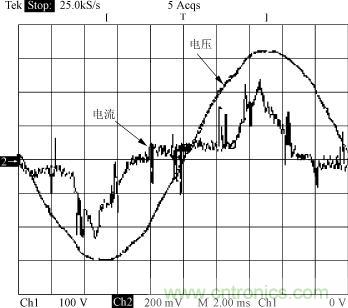

實驗測得,當輸入電壓為AC220V,50Hz,輸出功率為240W(240V/1A)時,系統的功率因數為0.786。轉換效率為72.5%。此時得到輸入端的電壓電流波形如圖4所示。

圖4:輸入電壓及電流波形

通過比較可知,在輸出功率相同的情況下,單級功率因數校正電路在功率因數校正能力和電源的轉換效率等方面,相對于兩級功率因數校正電路而言,相對要差一些。但隨著研究的深入,新的單級PFC拓撲結構和控制方案將不斷地被提出,單級PFC電路的性能也將逐步地得以完善。而單級功率因數校正電路體積小、電路簡單的特點使其成為AC-PDP開關電源小型化改造的一個首選方案。