使用低側柵極驅動器驅動MOSFET在照明、功率轉換、電磁閥驅動、電機控制和其他負載應用的地電壓不穩的系統中很常見。柵極驅動器能設計為可提供能高效驅動所需的高峰值電流。許多HVIC(高電壓IC)設備用來驅動半橋拓撲應用,因此包括一個低側柵極驅動器。為大多數應用設計并選擇低端柵極驅動器很簡單,只需基本了解驅動它們所需的功率MOSFET管的基本特征和驅動所需信號即可。盡管照明和阻性發熱等阻性負載可能在應用中占少數,但為簡潔性本文以驅動純阻性負載為列來做說明。

MOSFET的柵極電荷基本特性

MOSFET的柵極電荷參數反映了正常工作時區域的工作狀況。飛兆AN-7502功率MOSFET開關波形深入解釋了MOSFET在不同應用中相對應的不同區域。

在選擇合適大小的柵極驅動器時,與輸出電流能力的相關的MOSFET參數主要包括:

Qg(th) – 達到閾值電壓所需的柵極電荷

Qgs2 – 從閾值電壓到平臺電壓所需的柵極電荷

Qg(tot) – 達到徹底“導通”電壓的總柵極電荷

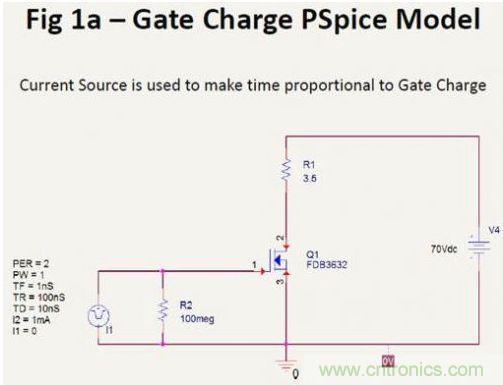

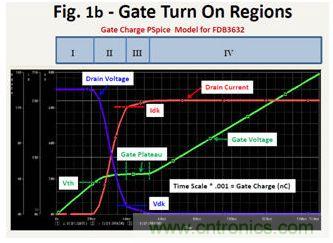

在圖1a中,Pspice模型中的1mA恒流源用于幫助創建帶阻性負載時導通期間典型柵極波形(圖1b)的曲線。柵極電荷與顯示的時間軸成正比,比例系數為0.001。可為良好建模的任何MOSFET輕松創建類似設備特定的曲線。

在區域I中,柵極電壓上升至Vth(柵極閾值電壓),然后MOSFET開始導通。區域I結束時的柵極電荷為Qg(th)。

[page]

在區域II中,柵極電壓上升至平臺區,漏極電壓達到Vdk(漏極膝點電壓)標志來到這一區域,同時漏極電流的上升斜率(dI/dt)顯著減小。在區域II中,不僅柵極驅動電路驅動柵極,而且源極電感和漏極至柵極的電容提供負反饋影響柵極的驅動。源極電感主要由MOSFET的綁定線(bond wires)和封裝引腳構成。實際使用中,此區域可能表現為高速振鈴。新的無引線MOSFET封裝往往具有更低的寄生電感,因此自電流快速變化帶來的影響也更小。區域II結束時的柵極電荷為Qg(th) + Qgs2。

在區域III或稱柵極平臺區(米勒平臺)域中,漏極的dV/dt減小。漏極電流的dI/dt也相應減小。注意電壓和電流波形中的膝點Vdk和Idk。在區域III中,柵極電荷增加,但柵極電壓幾乎不變,直到器件達到完全導通狀態。區域III結束時的柵極電荷通常不由制造商標出。

在區域IV中,也就是在柵極平臺區后,增大柵極電壓將繼續降低導通電阻Rds(漏極至源極電阻)。在特定柵極電壓和環境溫度下達到已知Rds點所需的柵極電荷標為Qg(tot)。對于標準柵極器件來說,這通常為10V,而對于邏輯電平器件來說,為4.5至5V。用于特定低電壓開關應用中具有較低閾值的MOSFET的柵極電壓則有所不同。

如Rds(漏極至源極電阻) 和Vth (柵極閾值電壓)等MOSFET的參數將隨溫度而變化,這在大多數設計中都很重要。但是,柵極電荷參數不那么依賴半導體工藝處理,而更多地與裸片幾何尺寸相關,因此具有最小的溫度變化影響。

初始設計考量

通常,設計人員需要先確定最小柵極驅動輸出要求。柵極驅動電路必須能夠在一段既定的時間內提供所需的Qg(tot)。其次,必須減少區域II和III上的轉換時間以最大程度地減少開關損耗。

柵極驅動器標出了多個參數,以幫助設計人員根據這些要求確定驅動器的大小。在固定容性負載下,吸入Isink和輸出Isource電流能力在對應Vdd/2或中值電壓點時標出。同樣標有上升和下降時間。在某些情況下,負載特性可能需要不同的導通和關斷能力。盡管MOSFET的Vth通常比用于驅動柵極的Vdd小,柵極Rg上的電壓在關斷期間的柵極平臺區較低。因此, 許多低側柵極驅動器為比高側驅動器設計得有更強的的電流能力來補償Rg上電壓的降低帶來的影響。

額定電流值是柵極驅動器選擇中的主要參數。實際上,柵極驅動器系列通常用額定電流值來區分。飛兆提供1、2、4和9A的低電壓系列。

第二重要的因素包括在多通道器件中的傳導延遲,傳導匹配柵極驅動器的輸出驅動能力也受到裸片和封裝的總熱耗散能力搜限制,同時也受到開關頻率的影響。

相關閱讀:

原創經典:開關電源設計中MOSFET驅動技術圖解

http://hdh-sz.com/power-art/80021287

基于MOSFET的高能效電源設計

http://hdh-sz.com/power-art/80020873

鋰電池短路保護:功率MOSFET及驅動電路的選擇與設計

http://hdh-sz.com/cp-art/80021668