【導讀】基于四個標準電壓電平的定義(進一步定義為配電接口)并依照每個應用的要求,本文提出了一種創新方案,從而構建最優的電源管理網絡(PMNet)。最后,本文對該方案的優勢進行了闡釋,穩壓器的供應商或者設計者、SoC集成器和系統制造商皆能從中受益。

在當今M2M(機對機)連接整個世界的黃金時代,物聯網能夠指定無所不在的“智能物”,實現物與物、設備或與其他對象之間的連接。典型的物聯網應用為可穿戴式設備和智能家電。

隨著智能便攜設備的功能日益增多、尺寸愈來愈小,應用于物聯網的系統級芯片(SoC)正面臨著指數復雜性、嚴峻的功耗(動態功耗和漏電)挑戰和低物料清單(BoM)成本的要求。服務于物聯網應用的無晶圓廠設計公司正借助于各種技術以降低總體功耗,其中包括動態電壓頻率調節 (DVFS)、多電壓電源域和狀態保持功能等。

實現超低功耗的關鍵在于,根據不同的電壓或電源域對SoC或子系統的架構做出正確定義;同時借助電源管理網絡(PMNet)的集成,實現低功耗技術并降低物料清單(BoM)成本。

電源管理網絡(PMNet)包括所有的穩壓元件(穩壓器、無源濾波元件,電網及其寄生元件等物理網),上至電源、下至SoC或子系統的每一類負載/塊體所用到的元件。電源管理網絡架構針對SoC的每個負載都進行了自下而上的優化,所采用的庫是是幾乎不可以重復使用的。有多少應用,就可能有多少數量的電源管理網絡。因此,SoC集成器所面臨的主要挑戰之一就是依照每個應用的要求,選擇相適應的電源管理網絡(PMNet)架構,同時嵌入合適的穩壓器。

基于四個標準電壓電平的定義(進一步定義為配電接口)并依照每個應用的要求,本文提出了一種創新方案,從而構建最優的電源管理網絡(PMNet)。最后,本文對該方案的優勢進行了闡釋,穩壓器的供應商或者設計者、SoC集成器和系統制造商皆能從中受益。

DELTA:可重復使用的電源套件庫(RPKL)的突破性方案

一項復雜的SoC設計需要諸多定制穩壓器,如果采用如此多的穩壓器,將會增加設計或者采購成本,也會延長上市時間。而RPKL方案則與之不同,海豚集成推薦將該方案運用于SoC集成器,以便:

·通過設計或者獲取一套可重用組件,可以控制從庫交換格式凍結(LEF-freeze)到流片的交付時間,從而縮短產品上市周期。

·實現多種優化(例如:高效率、低噪、低物料清單和低漏電等),針對每個標準采用經過精簡的元件組。

·實行標準化的PMNet集成規則,以便PMNet能夠整合來自競爭對手和合作伙伴的集成器,同樣適用于無縫集成和裝配。

RPKL方案也引入了優值(FoM)的概念,從而依照每個應用的要求來選擇最優的PMNet。對于不同的定制穩壓器,用戶往往會進行性能上的比較;對于PMNet,用戶往往不清楚如何進行整體上的比較。最重要的是,應用常常是針對于不同優化之間的特定權衡:比如低功耗、低物料清單或者低噪。借助共同的優值(FoM),用戶則可以從諸多選擇中選擇最佳的PMNet。

優值(FoM,越低越好) 是任意函數關于各種參數的分配權重,用以優化各種性能。SoC集成器僅需在以下要素之間實現性能的權衡:面積、BoM、漏電和動態功耗等。

采用FoM進行PMNet基準測試的這一案例將在本文后續部分進行分析。

標準化配電接口(IDP)的必要性

為了定義具備可重用性和靈活性的集成器,十分有必要采用預先定義的標準化配電接口(IDP)。通過該接口,電力能夠分配到不同的電源島或者負載。一對一的連接則為供電接口(IAP)。

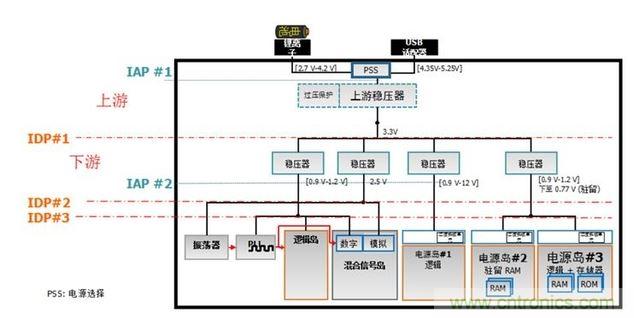

一旦對配電接口做出了定義,就可以劃分上游和下游穩壓器的穩壓限制。配電接口電平是由限制電壓范圍和最大噪聲頻譜所定義的,下游穩壓器及其負載則能夠承受該頻譜。如圖表1所示,上游穩壓器直接同電源(鋰離子電池或USB 5伏)相連接,故而需要高電壓保護;而下游穩壓器則與負載相連接,可以進行優化以滿足每個負載或電源域的要求(例如射頻或模擬塊的低漏電和低噪音等)。同時也可以滿足以下要素之間的權衡:更高的轉換效率、面積、物料清單(BoM)和具備多個電源域的SoC對抗噪度的需求。

對這些配電接口(IDP)所下的定義是實現RPKL方案的必要條件,因為有助于構建可重復使用的穩壓器,有助于實現與內部或第三方穩壓器的平穩結合。

圖1:借助配電接口(IDP)實現上下游穩壓器的分離

“四大神獸”配電接口

在對各類物聯網應用(如智能電表、智能卡、智能手機、智能玻璃、平板電腦和智能手表)進行過大量的框圖分析之后,其中規格為180納米至28納米,可以得出結論:最少需要4個不同的配電接口電壓來構建一個RPKL。

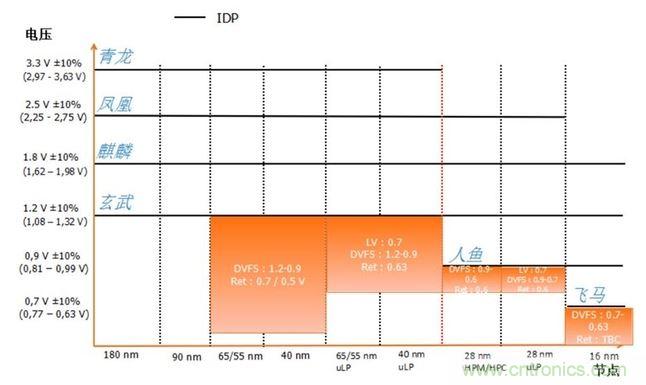

如圖表2所示,工藝節點為180納米至40納米,電壓分別為1.2伏、1.8伏、2.5伏和3.3伏。對于28納米和16納米而言,需要4個電壓電平不同的配電接口。通過這些配電接口,為穩壓器輸入和輸出電壓設立了標準。

選擇4個不同電壓的原因如下:

·系統常用電壓、電源輸入/輸出和外圍設備的工藝節點為180納米,90納米,65納米,40納米及以下

·沒有高于3.3伏(+/- 10%) 、低至40納米的配電接口(IDP)避免為下游穩壓器提供高電壓保護,從而實現硅面積的最小化

·基于這些配電接口,而非具有不同互聯電壓的定制穩壓器,可以實現穩壓器的整體優化

·增添一個IDP不能為PMNet帶來更佳的整體優化,但是會給RPKL增加多余的穩壓元件

圖2:每個技術工藝的配電接口(IDP)電壓電平

借助RPKL與標準配電接口(IDP)實現系統級芯片(SoC)的整體優化

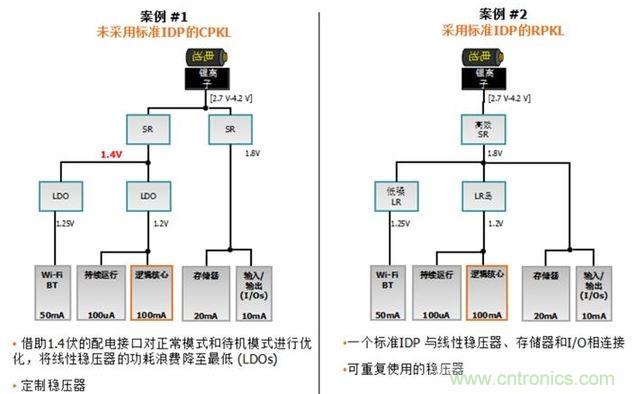

以一款智能手表應用的案例(如圖表3所示的簡化框圖)來說明RPKL(基于所定義的4個IDP)和定制穩壓器(即CPKL定制電源套件庫,電壓電平為1.4伏,以便對穩壓器進行級聯)之間的不同。

假定SoC在99%的使用時間內都處于待機模式(只有持續運行塊(always-on block)處于工作狀態)。為了將平均功耗和硅面積降至最低,可以采用簡化的FoM,即平均功耗和嵌入式穩壓器硅面積的乘積。(FoM=毫瓦小時*平方毫米)。在兩個案例當中,假定開關穩壓器(SR)的功率效率皆為80%。

圖3:對具備與不具備標準IDP的PMNet架構所進行的比較

[page]

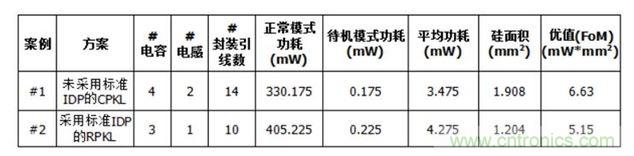

表1就以下要素總結了兩個案例所存在的性能差別:物料清單(BoM)、硅面積、功耗和FoM值。

表1:兩個案例的FoM對比

借助FoM,RPKL方案給出了功耗和硅面積之間的最佳權衡。與CPKL解決方案相比,RPKL方案大大縮減了面積,減少了平均功耗和物料清單(BoM)(元件數量與封裝引腳數)。

這一案例可以說明,借助經過定義的IDP并基于每個應用的要求,RPKL方案對SoC而言極具優勢;此外也可以說明,有必要在優化PMNet的過程中同時納入多個標準。

借由標準配電接口(IDP)電壓范圍實現準確預算

作為標準單元庫,IDP由10%的精度范圍所定義。雖然可能看似微不足道,但是10%的精度范圍能夠實現以下預算:

·對于穩壓器輸出電壓,標準“直流(DC)精度”為3%,以下要素考慮在內:工藝-電壓-溫度(PVT)的變化,負載穩壓和線性穩壓

·標準的“模式轉換(MT)精度”為4%,其中包括負載瞬態和輸出紋波所造成的干擾

·關于SoC集成預算,標準“最低IR壓降(IR Drop)”為3%:

在一般情況下,穩壓器的最低壓降為0.2伏;

在布局與布線(P&R)位于電源和上游穩壓器、或者上下游穩壓器之間的情況下,IR壓降(IR Drop)的預算至少為3%。SoC集成器可以在一定程度上自由定義所能接受的路由長度和寬度,而不會損耗最終系統的性能,這取決于該接口的電流/電壓特性和路由的寄生電阻。

借助這些預算所取得的主要突破有:

·借由標準直流(DC)和模式轉換(MT)的精度,能夠促進上下游穩壓元件與內部或第三方穩壓元件之間的結合,以及/或者SoC的內部或外部負載。

·IR壓降(IR Drop)預算的標準容差能夠減少前端設計和后端P&R之間的迭代。

完整的電源管理方案,RPKL穩壓元件以及更多

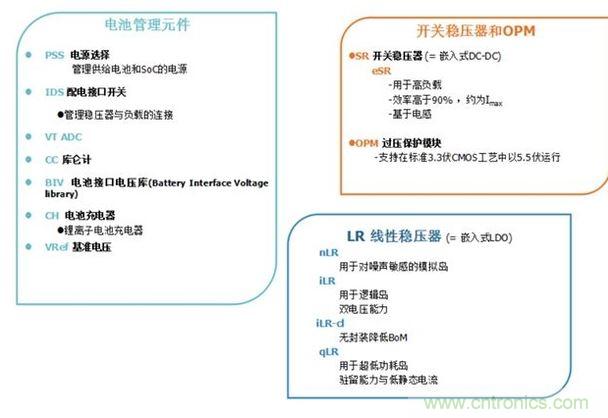

基于RPKL方案,海豚集成推出了DELTA穩壓元件庫,如圖表5所示,該庫由電池管理組件、開關穩壓器和線性穩壓器所組成。就每個穩壓元件而言,可以為系統級驗證提供先進的視圖(仿真模型),從而將性能下降的風險降至最小化,該風險源于SoC運行模式的過渡和通過PMNet所傳播的各類噪聲。

圖4:DELTA穩壓元件產品

除了能夠構建最優的PMNet、降低SoC功耗的DELTA產品之外,海豚集成還提供了超低漏電存儲器(漏電降幅達1000倍)和超低漏電標準單元庫(降幅達750倍),能夠直接與電池相連,從而滿足SoC在漏電方面的要求。

共贏

本文闡釋了可重復使用的電源套件方案以及運用于電源分配的四個預定義電壓電平的必要性和優勢。這四個IDP和電壓精度,有助于設置穩壓元件的直流精度、SoC的IR壓降(IR Drop)預算和交流容差, 原因在于PMNet的模式轉換。

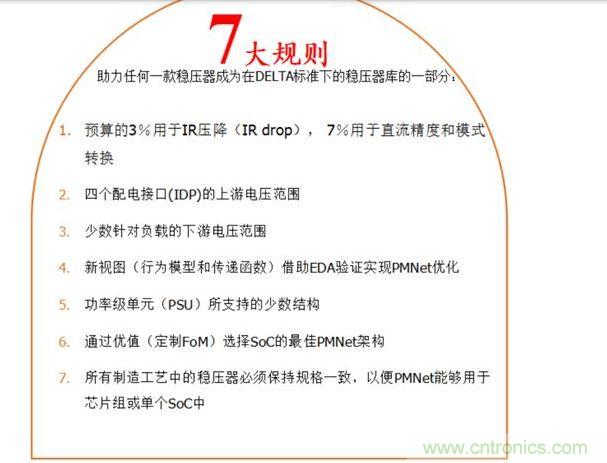

海豚集成與您分享七大規則(見圖表5),這也是DELTA產品所遵循的規則。

圖5:DELTA標準的七大規則

在七大規則的指導下,PMNet解決方案能夠在最大程度上縮短上市時間(借助可重復使用的元件),實現不同優化標準之間的最佳權衡(借助FoM和標準化的分級裝配規則)和最佳系統級風險管理(借助高級視圖和EDA驗證)。

遵循這些規則,任何一款穩壓器都可以成為強大的PMNet解決方案的一部分并且受益其中(詳見圖表6的總結),從而達到投資回報的極致。

圖6:完整的PMNet解決方案