【導讀】當電源與其負載突然斷開時,電路寄生電感元件上的大電流擺動會產生巨大的尖峰電壓,對電路上的電子元件造成十分不利的影響。與電池保護應用類似,此處MOSFET可以將輸入電源與其他電路隔離開來。但此時,FET的作用并不是立即斷開輸入與輸出之間的連接,而是減輕那些具有破壞力的浪涌電流帶來的嚴重后果。這需要通過一個控制器來調節輸入電壓(VIN)和輸出電壓(VOUT)之間MOSFET上的柵源偏壓,使MOSFET處于飽和狀態,從而阻止可能通過的電流(見圖1)。

圖1:簡化的熱插拔電路

首先要為FET考慮的是選擇合適的擊穿電壓,一般為最大輸入電壓的1.5到2倍。例如,12V系統通常為25V或30V FET,而48V系統通常為100V或在某些情況下達到150V FET。下一個考慮因素應該是MOSFET的安全工作區(SOA),如數據表中的一條曲線。它特別有助于指示MOSFET在短時功率浪涌期間是如何影響熱擊穿的,這與在熱插拔應用中必須吸收的情況并無二致。由于安全操作區域(SOA)是進行適當選擇最重要的標準,請參照了解MOSFET數據表-SOA圖,該文詳細介紹TI如何進行測量,然后生成設備數據表中顯示的MOSFET的SOA。

對于設計師而言,關鍵的問題是FET可能會經受的最大浪涌電流(或預計會限制到輸出)是多大,以及這種浪涌會持續多久。了解了這些信息,就可以相對簡單地在設備數據表的SOA圖上查找相應的電流和電壓差。

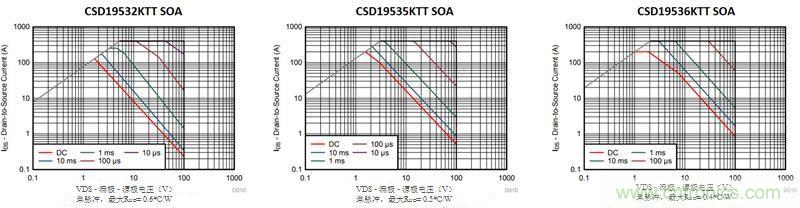

例如,如果設計輸入電壓為48V,并且希望在8ms內限制輸出電流不超過2A,設計師可以參考CSD19532KTT、CSD19535KTT和CSD19536KTT SOA的10ms曲線(圖2),并推斷出后兩種設備可能行得通,而CSD19532KTT則不行。由于CSD19535KTT已經擁有足夠余量,對此種應用來說,更昂貴的CSD19536KTT可能提供過高的性能。

圖2:三種不同100V D2PAK MOSFET的SOA

假定環境溫度為25?C,與在數據表上測量SOA的情況相同。由于最終應用可能暴露于更熱的環境中,所以必須按照環境溫度與FET最大結溫之比,按比例為SOA降額。例如,最終系統的最高環境溫度是70?C,可以使用公式1為SOA曲線降額:

在這種情況下,CSD19535KTT的10ms,48V能力將從?2.5A降至?1.8A。由此推斷出特定的FET可能不再適合該應用,從而設計師應該改選CSD19536KTT。

值得注意的是,這種降額方法假設MOSFET恰好在最大結溫下發生故障,雖然通常不會如此。假設在SOA測試中測得的失效點實際上發生在200?C或其他任意較高溫度下,計算的降額將更接近統一。也就是說,這種降額方法的計算不是保守的算法。

SOA還將決定MOSFET封裝類型。D2PAK封裝可以容納大型硅芯片,所以它們在更高功率的應用中非常流行。較小的5mm×6mm和3.3mm×3.3mm四方扁平無引線(QFN)封裝更適合低功率應用。為抵御小于5 - 10A的浪涌電流,FET通常與控制器集成在一起。

以下是幾個注意點:

當針對熱插拔應用時,對于FET在飽和區工作的任何情況,設計師都可以使用相同的SOA選擇過程,甚至可以為OR-ing應用、以太網供電(PoE)以及低速開關應用(如電機控制)使用相同的FET選擇方法,在MOSFET關斷期間,會出現相當高的VDS和IDS的重疊。

熱插拔是一種傾向于使用表面貼裝FET的應用,而不是通孔FET(如TO-220或I-PAK封裝)。原因在于短脈沖持續時間和熱擊穿事件發生的加熱非常有限。換句話說,從硅結到外殼的電容熱阻元件可以防止熱量快速散失到電路板或散熱片中以冷卻結點。芯片尺寸的函數 - 結到外殼的熱阻抗(RθJC)很重要,但封裝、電路板和系統散熱環境的函數 - 結到環境熱阻抗(RθJA)要小得多。出于同樣的原因,很難看到散熱片用于這些應用。

設計人員經常假定目錄中最低電阻的MOSFET將具有最強的SOA。這背后的邏輯是 - 在相同的硅片生產中較低的電阻通常表明封裝內部有較大的硅芯片,這確實產生了更好的SOA性能和更低的結至外殼熱阻抗。然而,隨著硅片的更新迭代提高了單位面積電阻(RSP),硅片也傾向于增加電池密度。硅芯片內部的單元結構越密集,芯片越容易發生熱擊穿。這就是為什么具有更高電阻的舊一代FET有時也具有更好SOA性能的原因??傊?,調查和比較SOA是非常有必要的。

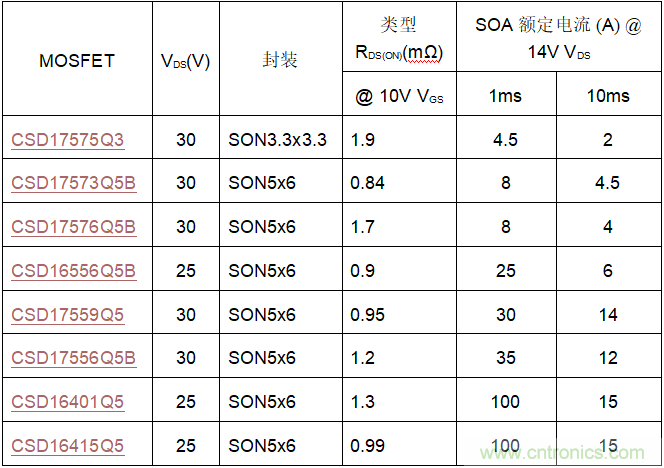

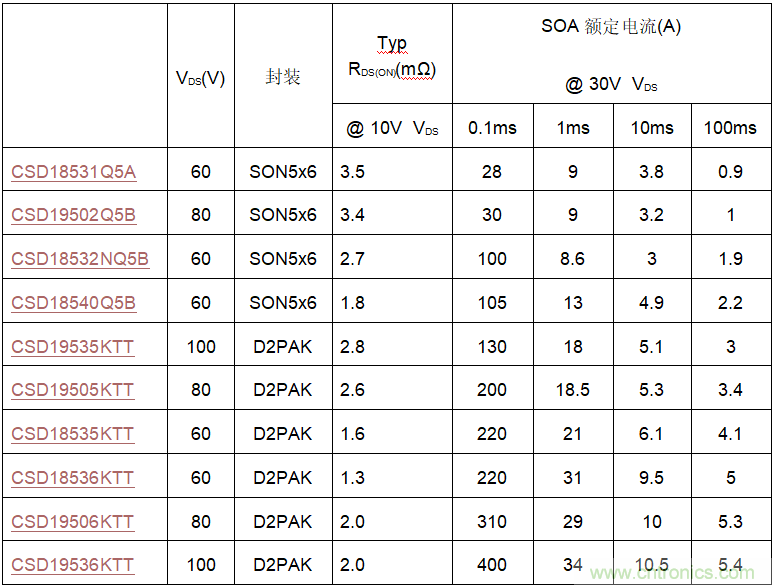

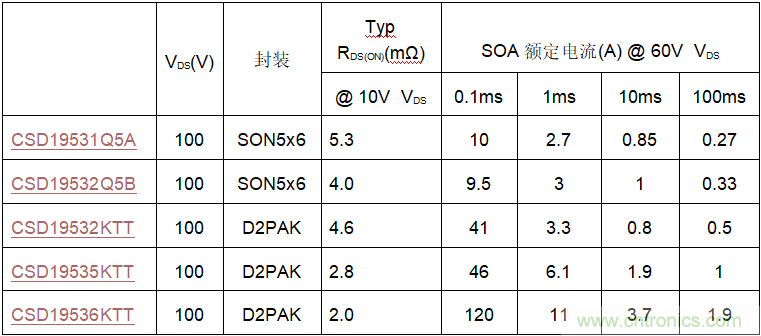

請在TI官網了解更多各種熱插拔控制器的信息。本文末尾的表1-3重點介紹了用于熱插拔的一些設備,它們為SOA功能提供了部分參考值。

更多信息請查閱MOSFET選項博客系列。

表1:用于12V熱插拔的MOSFET

表2:用于24V熱插拔的MOSFET

表3:用于48V熱插拔的MOSFET

推薦閱讀: