【導讀】作為一種復雜的集成電路,FPGA系統供電的電源的設計與一般的電子系統相比,要求也更高,需要具備高精度、高密度、可控性、高效及小型化等的特點。本文系統介紹了FPGA電源的不同特性,同時會通過實例,讓工程師更深入地了解各特性的意義,以及FPGA規范約束及其對電源設計的影響,以便快速完成FPGA系統的電源設計。

前言

FPGA (Field Programmable Gate Arrays) 是現今最復雜的集成電路之一。它們采用先進的晶體管技術和芯片架構實現高性能、小體積的高端產品,而為FPGA系統供電的電源與一般的電子系統相比,要求更高。

隨著市場上對FPGA系統應用的普及,對其電源解決方案的需求也越來越旺盛,FPGA電源系統除了需要滿足基本要求外,還需要具備高精度、高密度、可控性、高效及小型化等的特點。

現實中,工程師希望將大部分時間花在編程上,而不想花太多的時間和精力考慮如何設計合適的電源耗材。所以在本文中,我們會介紹FPGA電源的不同特性,同時會通過實例,讓工程師更深入地了解各特性的意義,以及FPGA規范約束及其對電源設計的影響。

電壓精度

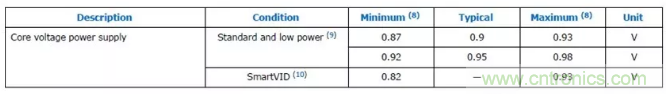

內核電源電壓 (Core Power Supply) 是平衡FPGA功耗和性能的最重要關鍵要素之一。規格書中一般會列出可接受的電壓范圍,但此范圍并不是完整的描述,對FPGA而言,電源電壓在滿足線路運作要求的同時,也需要權衡和優化。下圖一是以Intel的Arria 10 FPGA內核電壓要求為例,其也代表了其他FPGA內核的電壓要求。一般會顯示容差范圍額定電壓,例如Arria 10 FPGA為±0.03V,FPGA會在這個電壓窗口內運行得很好,但實際情況比圖片顯示復雜很多。

事實上,FPGA可以在不同電壓下工作,這具體取決于其特殊的制造公差以及所采用的特定邏輯設計。即使是同一電壓要求,一個FPGA所需的靜態電壓也可能是與另一個FPGA不同,所以在電源設計時必須要考慮對應FPGA的動態與靜態之間的變化而自行調控。

圖1:Arria 10 FPGA內核電壓要求 (來源: Intel®Arria® 10 器件數據表)

動態功率和靜態功率

設計合適的FPGA電源方案,目標是產生恰當的性能水平來操作編程功能,減少不必要的功耗。我們從半導體物理學的角度看,動態和靜態功率都隨著內核VDD的增加而顯著增加,因此我們的目標是讓FPGA有足夠電壓來正常運行,以滿足其時間要求——因為過量功耗不但對提高性能沒有任何幫助,相反它會令晶體管漏電流隨著溫度的升溫,消耗更多的不必要的電力。由于這些原因,當務之急是優化設計和工作點的電壓。

該優化過程需要非常精確的電源才能獲得成功。如果內核電壓低于要求,則FPGA可能由于時序錯誤而發生故障。如果內核電壓漂移超過最大規格,可能會損壞FPGA,或者可能會在邏輯中產生保持時間故障。所以,必須考慮電源容差范圍來防止所有這些情況,并且僅保證保持在規格限制內的指令電壓。

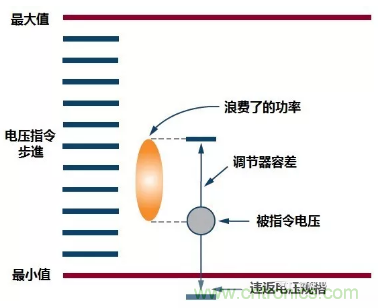

問題是大多數電源調節器都不夠準確。調節電壓可以在被指令電壓附近的公差范圍內的任何地方,并且它可以隨負載條件、溫度和老化而漂移。±2%容差的電源即表示可以在4%的電壓范圍內輸出任何值。為了補償電壓處于2%過低的可能性,被指令電壓必須比滿足時序所需的電壓提高2%。如果經過調節器后電壓漂移到高于被指令電壓2%處,它將比該工作點所需的最小電壓運行高4%。這仍然符合規定的FPGA所需的電壓要求,卻浪費了大量功率,如下圖2所示。

圖2:電源調節器容差權衡

解決這一問題的方案是選擇能夠以更嚴格的電壓容差運行的電源調節器。使用具有±0.5%容差的調節器,可以在所需的工作頻率下、更接近所需的最小規格內工作,并且保證與所需的電壓相差小于1%。這樣,好讓FPGA在最小功耗的情況下,正常工作。

高電量需求

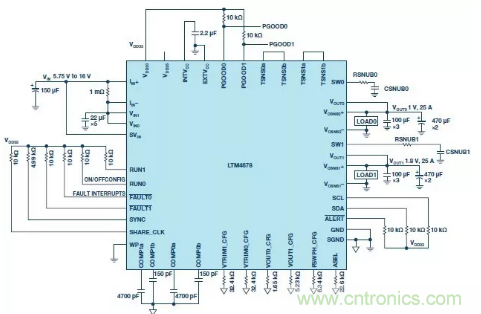

FPGA系統中的器件通常需要不同調節電壓,例如電壓的內核電壓處理器,其要求電壓可以是0.8V、1.0V、1.2V、1.5V或1.8V等。雖然是低電壓供應,但其密集的晶體管結構及長期保持高速運作的情況下,供電電源方案可能需要10A或以上,具體的處理器要求通常決定了其他電源要求,例如負載瞬態恢復、待機模式等,這需要負載點(Point-of-Load,或簡稱PoL)穩壓電源專為核心電壓設計。 PoL穩壓電源是一種高性能穩壓器,其各Vout電壓軌獨立于各自的負載設置。這有助于解決高瞬態電流的要求以及諸如FPGA高性能半導體器件的低噪聲要求。例如ADI 公司的LTM4678系列,包含兩組能夠同時提供高密度的電源供應輸出,分別為1V@25A 及1.8V@25V。

圖3:ADI的LTM4678應用線路圖

可控性需求

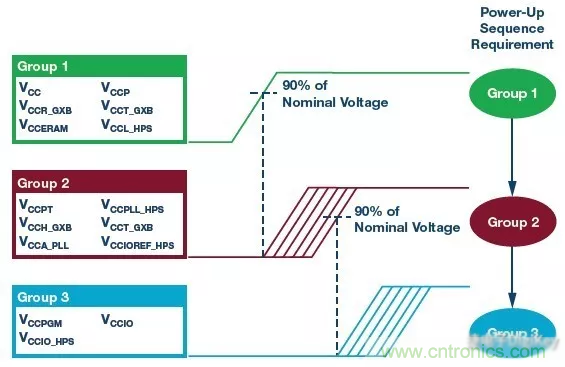

FPGA中含有大量而復雜編排的晶體管,一塊芯片包含數億個晶體管,當中被分割成可以設計并獨立管理的內核段、模塊段和隔斷。這些特定的編排是的其具有許多不同電源域,在電壓、電流、紋波和噪聲以外,還包括啟動、關斷和故障條件期間的序列順序,故可控性的FPGA電源需要妥善管理輸出的次序及其電量。

市場中較新的FPGA在規格中會提供針對啟動和關斷電源時的序列順序提出特定的要求,確保FPGA正常開啟及復位,保持最小的電流消耗,并在電源轉換期間將I/O保持在正確的三態配置下。再以Arria 10為例,其技術規格將電源分為三個序列組(1、2、3),并要求它們按升序排列為1、2、3,然后按相反的順序降序排列:3、 2、1。

圖4:Arria 10電源組順序示意圖

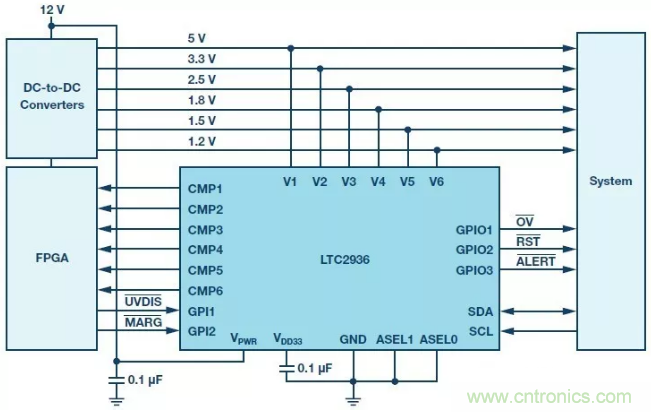

例如ADI公司的LTC2936可以提供六個可編程閾值模擬比較器,用于檢測快速事件并將數字狀態發送到邏輯。該器件還有三個可編程GPIO引腳,可提供額外的功能。該可編程IC包括EEPROM,后者可在啟動時近乎即時地工作;該IC還能通過其I2C/SMBus接口存儲故障遙測數據以便進行調試。

圖5:ADI的LTC2936應用方框圖

FPGA 開發套件支持

工程師可利用FPGA開發套件協助開發。例如Arria 10 SoC開發套件 (DK-SOC-10AS066S-A)展示了用于Arria 10 SoC 電源要求的ADI的LTM4677µmodule電源解決方案。

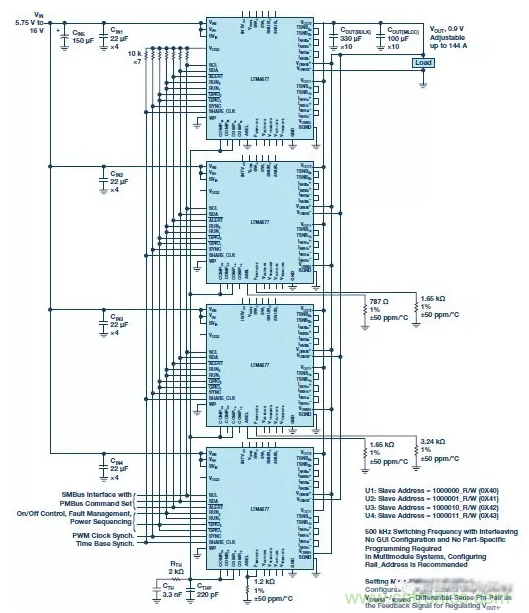

在套件中,內核電源的工作電壓為0.95V,工作電流為30A。由于這些電源要求相對寬松,單個LTM4677模塊就可輕松提供所需電流(最高36A)。對于要求更多電流且條件更為苛刻的應用,最多可以并行運行四個LTM4677模塊,以提供高達144A的電流,如圖7所示。

圖6:Arria10 SoC開發套件

圖7:利用四個LTM4677模塊并聯的應用電路圖,可提供高達144A的電流

利用參數列表選料

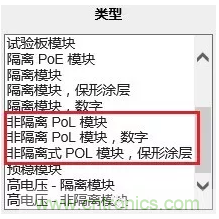

了解應用的要求之后,工程師可在Digi-Key官網上,在「電源 - 板安裝」分類中,選擇「直流轉換器」子分類。「應用篩選程序」中,工程師可在「類型」中找到「POL」,或直接在「在結果中搜尋」中輸入「POL」以篩選PoL穩壓電源。

圖8

結 語

在FPGA系統中,電源解決方案是工程師需要考慮的重要題目之一。與一般的電腦要求不同,FPGA電源需要高精度、可編程功能、可調度等要素,及最重要的「高能量密度」,即低電壓/高電流。業界已將這類型的產品研發歸類于負載點(PoL)穩壓電源。

為方便工程師選料,Digi-Key官網上的「電源 - 板安裝」分類中的「直流轉換器」子分類中,在「類型」中已將PoL產品列出,方便工程師更快更準確地選料。

來源:得捷電子DigiKey

作者:Kevin Chow