【導讀】隨著通信、醫療和工業設備的總體尺寸不斷縮小,電源管理設計變得越來越重要。本文討論高度集成的全新電源管理解決方案的應用,這些新器件為RF系統、FPGA和處理器供電所帶來的優勢,以及有助于設計人員快速實現新設計的設計工具。

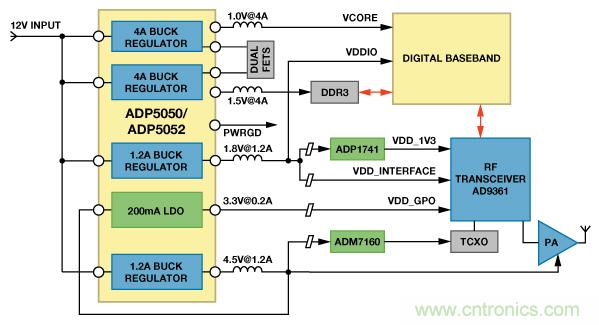

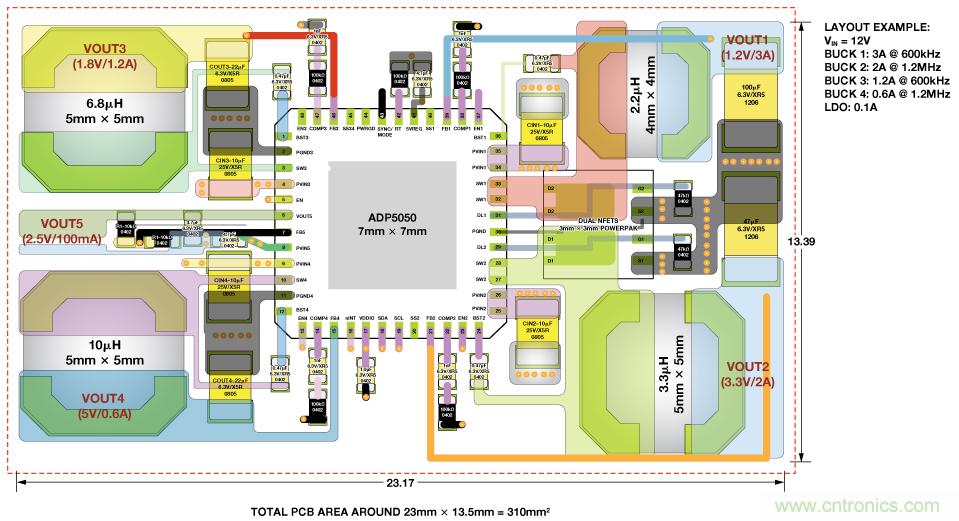

在通信基礎設施中,毫微微蜂窩和微微蜂窩的興起推動基站向更小型化方向發展,這對數字基帶、存儲器、RF收發器和功率放大器的供電提出了復雜要求,必須在最小的面積中提供最高的功率密度,如圖1所示。典型的小蜂窩系統需要密度非常高的電源,它能以快速瞬變響應輸送大電流以便為數字基帶供電,同時利用低噪聲、低壓差調節器(LDO)為AD9361RF捷變收發™、溫度補償晶體振蕩器(TCXO)和其他噪聲關鍵電源軌供電。將開關穩壓器的開關頻率設置到關鍵RF頻段以外可降低噪聲,并且同步開關穩壓器可確保拍頻不影響RF性能。降低數字基帶的內核電壓(VCORE)可將低功耗模式的功耗降至最低,電源時序控制則可確保數字基帶在RF收發器使能之前上電并運行。數字基帶與電源管理之間的I2C接口允許改變降壓調節器的輸出電壓。為提高可靠性,電源管理系統可以監控其自身的輸入電壓和芯片溫度,向基帶處理器報告任何故障。

圖1. 小型基站需要多種電源

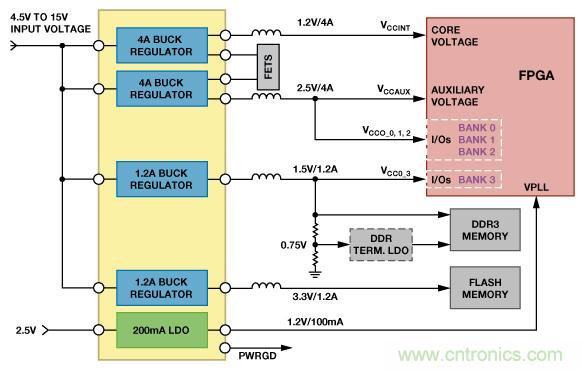

同樣,醫療和儀器設備(如便攜式超聲設備和手持式儀器)的趨勢也是尺寸越來越小,要求在更小的面積上以更有效的方式為FPGA、處理器和存儲器供電,如圖2所示。典型的FPGA和存儲器設計需要密度非常高的電源,它能以快速瞬變響應輸送大電流以便為內核和I/O電源軌供電,同時通過低噪聲軌為鎖相環(PLL)等片內模擬電路供電。電源時序至關重要,應確保FPGA在存儲器使能之前上電并運行。帶精密使能輸入和專用電源良好輸出的穩壓器支持電源時序控制和故障監控。電源設計師通常希望將同一電源IC用在不同應用中,因此,必須能夠改變電流限值。這種設計重用可大幅縮短產品上市時間——任何新產品開發流程中的關鍵要素之一。

圖2. 為基于FPGA的系統供電

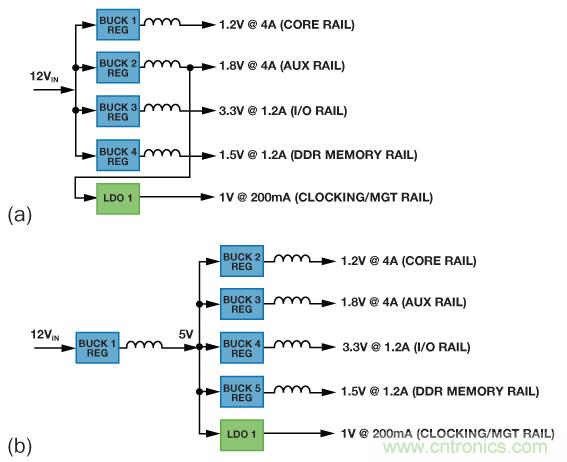

考慮具有1路12 V輸入和5路輸出的FPGA的多軌電源管理常見設計規格:

● 內核電軌:1.2 V (4 A)

● 輔助電軌:1.8 V (4 A)

● I/O電軌:3.3 V (1.2 A)

● DDR存儲器電軌:1.5 V (1.2 A)

● 時鐘電軌:1.0 V (200 mA)

典型的分立方案如圖3a所示,4個開關穩壓器連接到12 V輸入軌。一個開關穩壓器的輸出預調節LDO以降低功耗。另一種方法如圖3b所示,使用一個穩壓器將12 V輸入降壓至5 V中間軌,然后再經調節以產生所需的各個電壓。該方案的成本較低,但由于采用兩級電源轉換,效率也較低。在以上兩種方案中,各穩壓器都必須獨立使能,因此,可能需要一個專用電源時序控制器來控制電源的時序。噪聲可能也是一個問題,除非所有開關穩壓器都能同步以降低拍頻。

圖3. (a) 分立穩壓器設計,(b) 備選分立穩壓器設計

集成解決方案實現高效率、小尺寸

將多個降壓調節器和LDO集成到單個封裝中,可顯著縮小電源管理設計的總體尺寸。此外,與傳統分立方案相比,智能型集成解決方案具有許多優勢。減少分立元件數目可大幅降低設計的成本、復雜度和制造成本。集成電源管理單元(PMU)ADP5050 和 ADP5052可在單個IC中實現所有這些電壓和功能,所用PCB面積和元件大幅減少。

為了最大程度地提高效率,去除預調節器級,各降壓調節器均直接從12 V電壓供電(類似于圖3a)。降壓調節器1和2具有可編程電流限值(4 A、2.5 A或1.2 A),因此電源設計師可以快速輕松地為新設計改變電流,大大縮短開發時間。LDO可從1.7 V至5.5 V電源供電。在本例中,其中一個降壓調節器的1.8 V輸出為LDO供電,提供低噪聲1 V電源軌用于噪聲敏感的模擬電路。

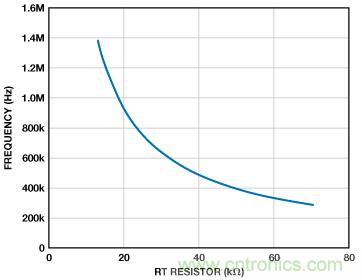

開關頻率fSW由電阻RRT設置,范圍是250 kHz到1.4 MHz。靈活的開關頻率范圍使得電源設計師可以優化設計,降低頻率以實現最高效率,或者提高頻率以實現最小的總體尺寸。圖4顯示了fSW 與 RRT之間的關系。RRT的值可通過下式計算:

RRT = (14822/fSW)1.081,R的單位為kΩ,f的單位為kHz。

圖4. 開關頻率與RRT的關系

某些設計中,兩者都很重要:對較高電流軌使用較低的開關頻率以提供最高電源效率,對較低電流軌使用較高的開關頻率以縮小電感尺寸和實現最小的PCB面積。ADP5050的主開關頻率具有二分頻選項,能夠以兩種頻率工作,如圖5所示。降壓調節器1和3的開關頻率可通過I2C端口設置為主開關頻率的一半。

圖5. ADP5050對高電流軌使用低開關頻率以提高效率,對低電流軌使用高開關頻率以縮小電感尺寸

電源時序控制

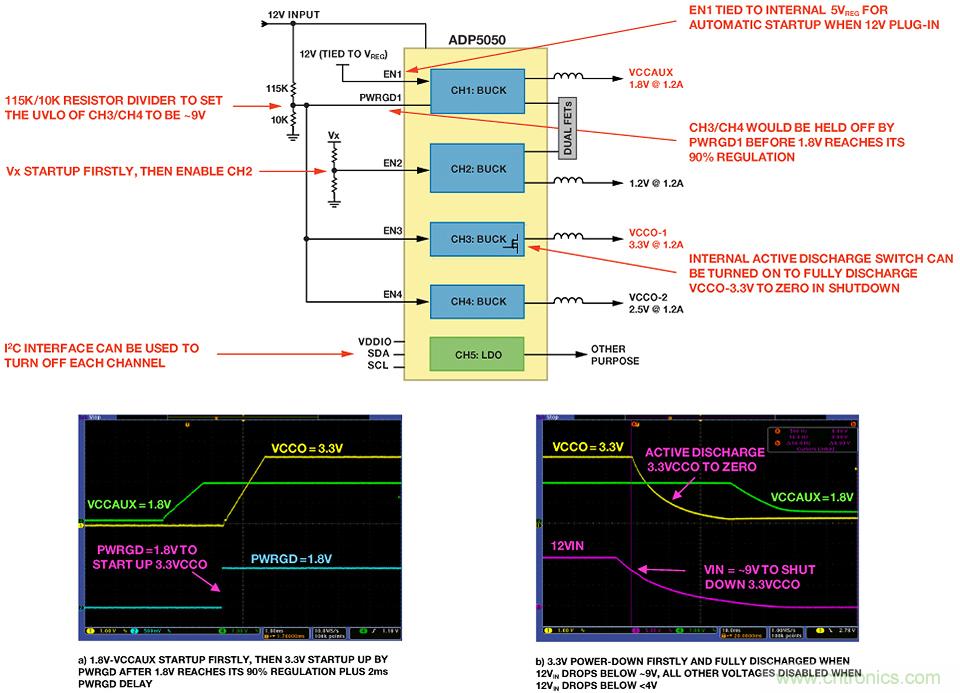

如圖6所示,ADP5050和ADP5052通過四個特性來簡化使用FPGA和處理器的應用的電源時序控制:精密使能輸入、可編程軟啟動、電源良好輸出和有源輸出放電開關。

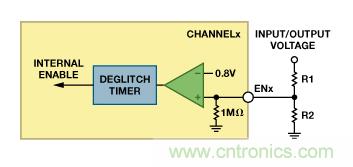

精密使能輸入: 每個穩壓器,包括LDO在內,都有一個帶0.8 V精密基準電壓的使能輸入(圖6-1)。當使能輸入的電壓大于0.8 V時,穩壓器使能;當該電壓小于0.725 V時,穩壓器禁用。內部1 MΩ下拉電阻可防止該引腳懸空時發生錯誤。利用精密使能閾值電壓,很容易控制器件內的電源時序,使用外部電源時也一樣。例如,降壓調節器1設置為5 V時,可以利用一個電阻分壓器來設置精確的4.0 V跳變點以使能降壓調節器2,依此類推為所有輸出設置精確的上電時序。

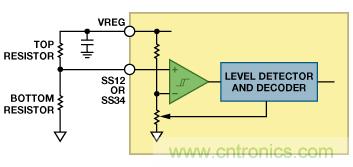

可編程軟啟動: 軟啟動電路以可控方式緩慢提高輸出電壓,從而限制浪涌電流。軟啟動引腳連接到 VREG時,軟啟動時間設置為2 ms;在軟啟動引腳與 VREG和地之間連接一個電阻分壓器時,軟啟動時間可提高至8 ms(圖6-2)。為了支持特定啟動序列或具有大輸出電容的值,可能需要這種配置。軟啟動的可配置能力和靈活性使大型復雜的FPGA以及處理器能以安全可控的方式上電。

1. 精密使能閾值: 高于0.8V使能穩壓器,低于0.72V(遲滯)則關斷穩壓器。

2. 可編程軟啟動: 各通道上的不同軟啟動可編程為2ms、4ms、8ms。

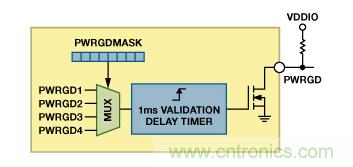

3. PWRGD輸出;CH1到CH4的所需PWRGDx可通過工廠熔絲或I2C配置。

4. 有源輸出放電開關可以接通輸出放電開關以縮短輸出電容的放電周期。

圖6. ADP5050和ADP5052簡化電源時序控制

電源良好輸出: 當所選降壓調節器正常工作時,開漏電源良好輸出(PWRGD)變為高電平(圖6-3)。電源良好引腳可以將電源的狀況告知主機系統。默認情況下,PWRGD監控降壓調節器1上的輸出電壓,但也可以定制其它通道來控制PWRGD引腳。各通道的狀態(PWRGx位)可通過ADP5050上的I2C接口回讀。PWRGx位的邏輯高電平表示調節輸出電壓高于標稱輸出的90.5%。當調節輸出電壓降至其標稱輸出的87.2%以下并持續50 μs以上時,PWRGx位設為邏輯低電平。PWRGD輸出是內部未屏蔽PWRGx信號的邏輯和。內部PWRGx信號必須為高電平且持續至少1 ms,PWRGD引腳才能變為高電平;如果任意PWRGx信號發生故障,則PWRGD引腳毫無延遲地變為低電平。控制PWRGD的通道(通道1至通道4)由工廠熔絲指定,或通過I2C接口設置相應位來指定。

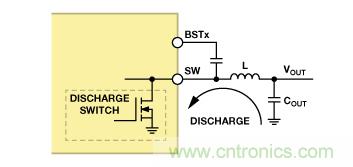

有源輸出放電開關: 每個降壓調節器均集成一個放電開關,它連接在開關節點與地之間(圖6-4)。當其相關調節器禁用時,開關接通,有助于使輸出電容快速放電。對于通道1至通道4,放電開關的典型電阻為250 Ω。當調節器禁用時,即使有大容性負載,有源放電開關也會將輸出拉至地。這樣就能顯著提高系統的穩定性,尤其是在周期供電時。

圖7所示為典型的上電/關斷時序。

圖7. 典型的上電/關斷時序

I2C 接口

The I2C 接口實現了對兩個降壓調節器輸出(通道1和通道4)的高級監控和基本動態電壓調整。

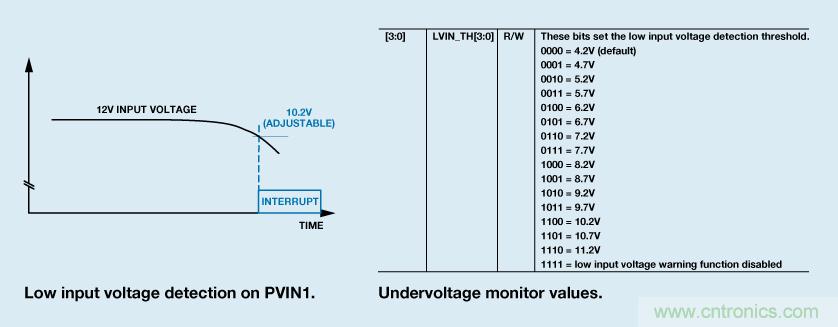

輸入電壓監控: 可以監控輸入電壓是否發生欠壓等故障。例如,將12 V電壓施加于輸入,I2C接口配置為:如果輸入電壓低于10.2 V,則觸發報警。專用引腳(nINT)上的信號告知系統處理器問題已出現,并關斷系統以便采取糾正措施。具備監控輸入電壓的能力可提高系統可靠性。圖8顯示了可以設置哪些值來監控ADP5050的輸入電壓。

圖8. 輸入欠壓檢測

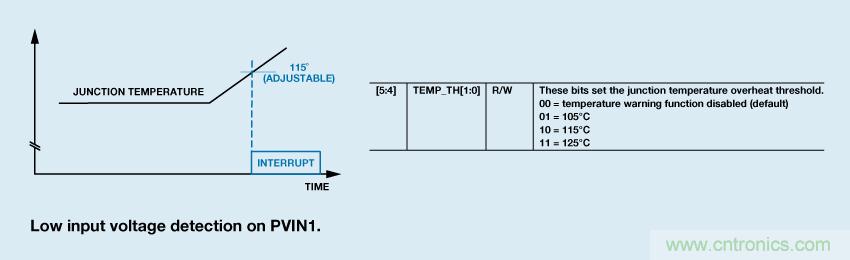

結溫監控:可以監控結溫以判斷是否發生過溫等故障。如果結溫高于預設值(105°C、115°C或125°C),nINT上就會產生報警信號。與熱關斷不同的是,此功能發送警告信號而不關斷器件。具備監控結溫并提醒系統處理器注意避免發生系統故障的能力可提高系統可靠性,如圖9所示。

圖9. 結溫監控

有源輸出放電開關: 每個降壓調節器均集成一個放電開關,它連接在開關節點與地之間(圖6-4)。當其相關調節器禁用時,開關接通,有助于使輸出電容快速放電。對于通道1至通道4,放電開關的典型電阻為250 Ω。當調節器禁用時,即使有大容性負載,有源放電開關也會將輸出拉至地。這樣就能顯著提高系統的穩定性,尤其是在周期供電時。

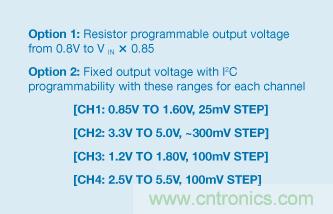

動態電壓調整:動態電壓調整通過動態降低低功耗模式下通道1和通道4的電源電壓來降低系統功耗,它也可以根據系統配置和負載動態改變輸出電壓。此外,所有四個降壓調節器的輸出電壓均可通過 I2C 接口設置,如圖10所示。

圖10. ADP5050輸出電壓選項

低噪聲特性

多個特性可降低電源產生的系統噪聲。

寬電阻可編程開關頻率范圍:RT引腳上的電阻可在250 kHz至1.4 MHz的范圍內設置開關頻率。電源設計師可靈活地設置開關頻率以避免系統噪聲頻段。

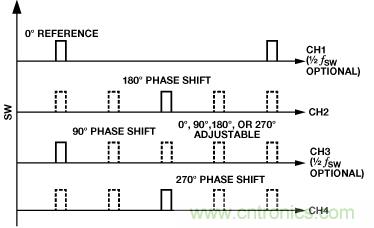

降壓調節器相移降壓調節器的相移可通過I2C接口設置。默認情況下,通道1和通道2之間以及通道3和通道4之間的相移為180°,如圖11所示。反相操作的優勢是輸入紋波電流和電源接地噪聲更低。

圖11. ADP5050/ADP5052的降壓調節器相移

圖12. 降壓調節器的相移可通過I2C接口配置

時鐘同步:開關頻率可通過SYNC/MODE引腳同步至250 kHz到1.4 MHz的外部時鐘。該能力對于RF和噪聲敏感應用很重要。檢測到外部時鐘時,開關頻率平滑過渡至其頻率。當外部時鐘停止時,器件切換到內部時鐘并繼續正常工作。與外部時鐘同步可使系統設計師遠離臨界噪聲頻段,并降低系統中多個器件產生的噪聲。

為成功同步,必須將內部開關頻率設置為接近于外部時鐘值的值,頻率差建議小于±15%。

通過工廠熔絲或I2C接口,可將SYNC/MODE引腳配置為同步時鐘輸出。當頻率等于內部開關頻率時,SYNC/MODE引腳產生占空比為50%的正時鐘脈沖。產生的同步時鐘與通道1開關節點之間有一個較短的延遲時間(約為 tSW)的15%)。

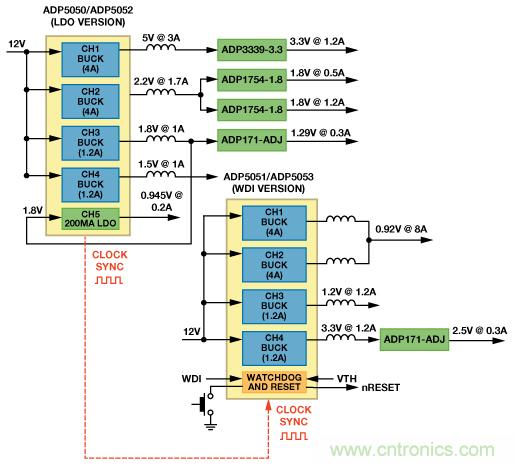

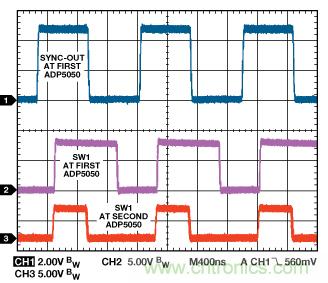

圖13顯示了兩個配置為頻率同步模式的器件:一個器件配置為時鐘輸出以同步另一個器件。應當使用100 kΩ上拉電阻,以防SYNC/MODE引腳懸空時發生邏輯錯誤。

圖13. RF應用顯示兩個器件同步以降低電源噪聲

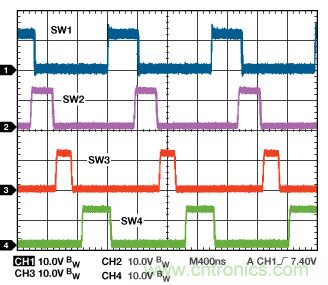

兩個器件均同步至同一時鐘,因此,第一個器件的通道1與第二個器件的通道1之間的相移為0°,如圖14所示。

圖14. 兩個以同步模式工作的ADP5050器件的波形

ADIsimPower 設計工具

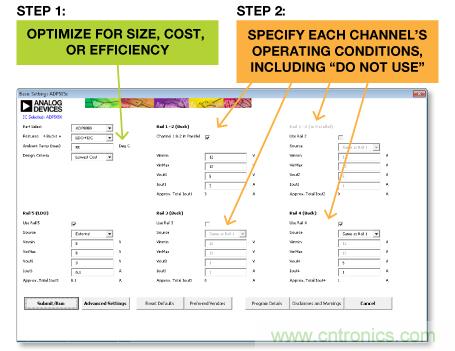

ADIsimPower™現在支持多通道高壓PMU ADP5050/ADP5052,這些器件從最高15 V的輸入為4/5的通道供電,每通道的負載電流最高可達4 A。憑借該設計工具,用戶可以級聯通道,將高電流通道并聯放置以形成8 A電源軌,考慮各通道的熱分布,從而優化設計。利用高級特性,用戶可以獨立指定各通道的紋波和瞬變性能、開關頻率、支持半主頻率的通道。

ADIsimPower允許用戶在圖15所示的軟件界面上快速輕松地輸入設計要求。

圖15. ADIsimPower軟件界面

軟件會智能選擇器件并生成完整的物料清單。評估板可以直接在該工具內申請。設計工具支持對各通道進行復雜的控制,如圖16所示。

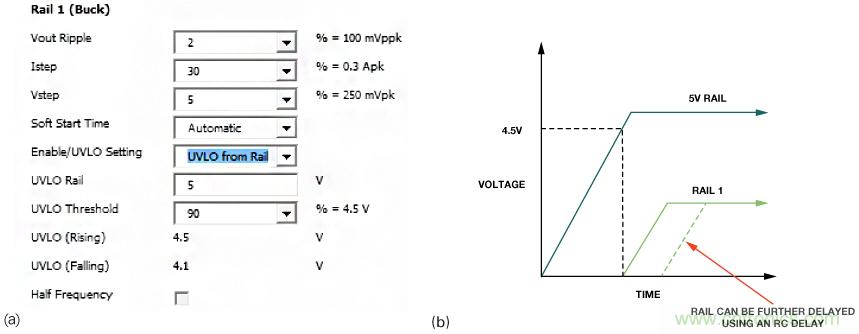

圖16. (a) 可以指定各軌的紋波、瞬變和響應。

(b) 使用精密使能的高級時序控制要求。

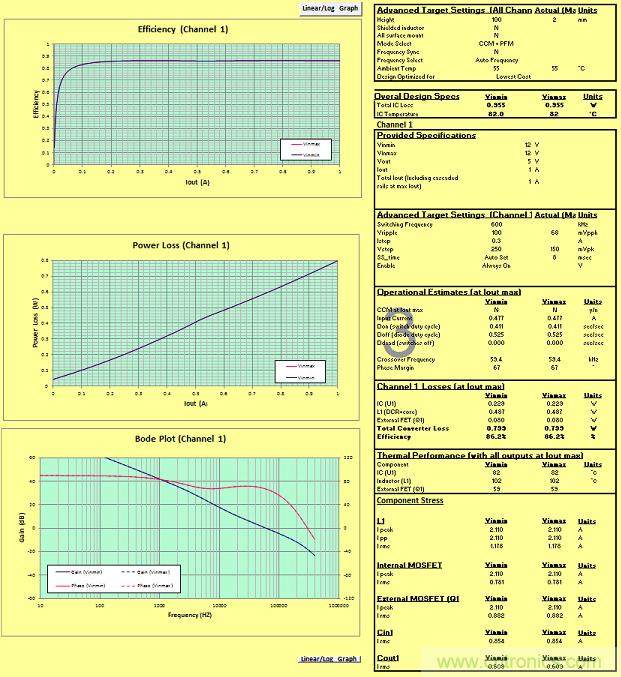

利用ADIsimPower,電源設計師可以快速獲得準確、經過測試的可靠性能數據,如圖17所示。

圖17. ADIsimPower仿真輸出

隨后便可在評估板上組裝設計,如圖18所示。

圖18. 使用ADP5050/ADP5052的電源電路

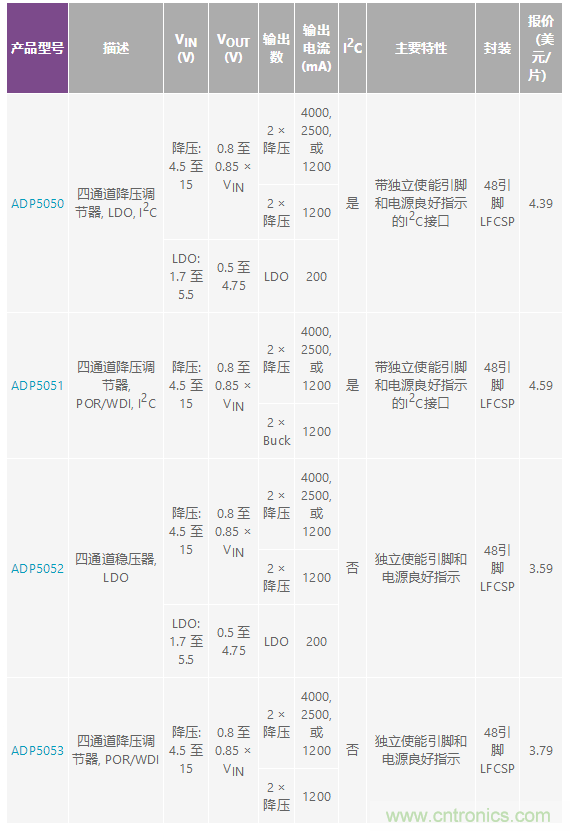

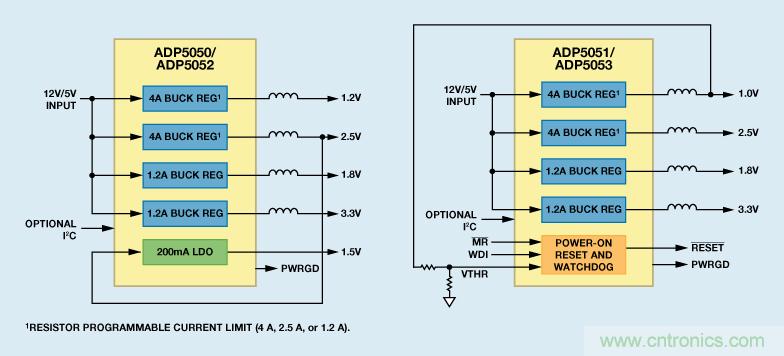

ADP5050/ADP5052/ADP5051/ADP5053 技術規格

圖19. ADP5050/ADP5051/ADP5052/ADP5053:四通道降壓開關調節器,帶LDO或POR/WDI,采用LFCSP封裝

結論

高度集成的全新PMU可實現具有高電源效率、高可靠性和超小尺寸的復雜電源管理解決方案。全新設計工具與靈活的集成電路相結合,則可縮短這些復雜電源產品的上市時間。ADP505x系列是ADI公司高度集成的多路輸出穩壓器的最新產品組合,該系列使單個IC能快速輕松地用于許多不同的應用,從而縮短電源設計時間。要討論這些器件的技術方面,請訪問EngineerZone中文技術論壇。

推薦閱讀: