【導讀】當IC輸出腳為低電平時,如果此器件不是驅動器, 而是一般器件,則由于輸出低電平電流太大, 遠大于器件手冊給出的值,輸出三極管將退出飽和區,進入工作區,使輸出低電平抬高很多。

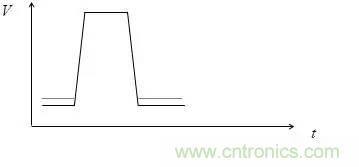

1、線電阻的電壓降的影響——地電平(0電平)直流引起的低電平提高

圖中虛線為提高的情況。提高幅度與IC的功耗大小、IC密度、饋電方式、地線電阻(R) 、饋電的地線總電流有關。 ΔV地= ΔI× ΔR

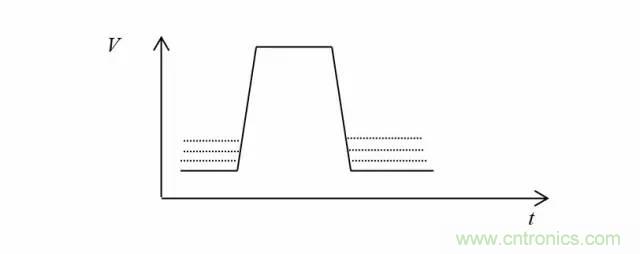

2、 信號線電阻的電壓降的影響

a) IC輸出管腳經過印制導線或電纜到另一IC的輸入腳,

輸出低電平電流在印制導線或電纜電阻上引起一個低電平的抬高,其值為ΔVOL=IOL×R 。 見圖中的上面一條虛線。

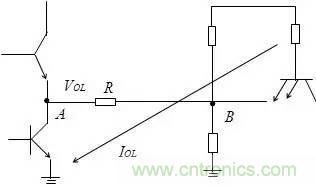

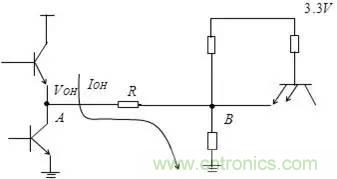

顯而易見,低電平的抬高與印制導線電阻值及輸出低電平電流有關,如下圖所示:

B點的低電平比A點的低電平高

注意:當IC輸出腳為低電平時,如果此器件不是驅動器, 而是一般器件,則由于輸出低電平電流太大, 遠大于器件手冊給出的值,輸出三極管將退出飽和區,進入工作區,使輸出低電平抬高很多。如下圖中上面一條虛線所示:

決定因素:端接方式

端接電阻大小

輸出管飽和深度

輸出管β值

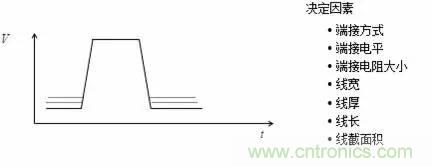

b) IC輸出管腳經過印制導線或電纜到另一個IC的輸入腳,輸出高電平電流在印制導線或電纜電阻上引起一個高電平的降低,其值為ΔVOH=IOH× R,見下圖中高電平上的下面虛線:

IOH由下列因素決定:端接方式、端接電平、端接電阻大小

R由下列因素決定:線寬、線厚、線長

顯而易見,高電平的降低與印制導線或電纜電阻值及輸出高電平電流有關,如下圖所示:

B點的高電平比A點的高電平要低

注意:IC輸出腳為高電平時, 如果此器件不是驅動器,而是一般器件, 則由于輸出高電平電流太大,遠大于器件手冊給出的值時,輸出管也會退出飽和區,進入工作區,使輸出高電平降低很多。如下圖中下面一條虛線所示:

3、電源線電阻的電壓降的影響

IC的電源電壓(如+3.3V),如果系統中存在差值,當小于+3.3V時, 輸出高電平將產生一個下降值, 如上圖中高電平上的虛線所示:

由于系統電源有集中電源和分散的電源模塊之分,此差值不同,由于IC功耗的大小、IC密度、饋電方式、電源線的饋電電阻值以及電源電流值,引起一個 ΔVCC (ΔVCC =ΔI×ΔR)

以上原因,使TTL信號波形變得離理想波形很遠了。 低電平大為提高了,高電平也大為降低了。 對這些值若不嚴加控制, 對系統工作的穩定可靠工作是不利的。此外,結溫差,即不同功耗的器件的P-N結的溫度不同,還會影響高低電平及門檻電平的變化也會影響系統工作。

除上面所說的直流成分之外,更為重要的是系統是以極高頻率在工作,也就是說, 系統內的器件、導線有各種頻率的, 各種轉換速率的信號在動作、傳遞。 首先是相互之間的信號電磁藕合 (串擾) 和信號在不同特性阻抗傳輸路徑上的反射, 以及電源, 地電平由于IC高頻轉換引起電流尖峰電平,使TTL信號波形變得更壞。

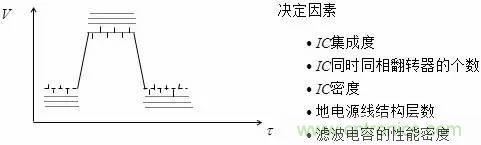

4、轉換噪聲

由于系統工作時,器件以高頻轉換,造成供電系統上有高頻率變化的電流尖峰,而供電的電源線路和地線路都可看成是很小的電阻、電感、電容元件。電流尖峰值太大, 在它們上面會產生較大的交流尖峰電壓,其電源上的尖峰電壓基本上會串擾到高電平上,而地電平上的尖峰電壓會串擾到低電平上,如下圖所示:IC內部同樣存在這種尖峰電壓。

5、串擾噪聲

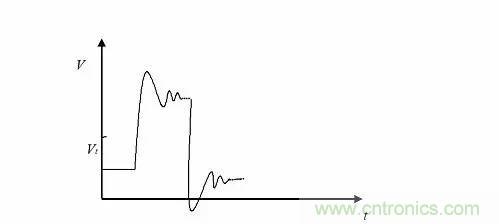

由于系統組裝越來越密, 印制導線之間的距離越來越近,鄰近導線上有高速轉換的電平信號。 如正跳變信號跳變的時間tr和負跳變的時間tf都很小,使得導線上已有信號上疊加一個較大的電磁藕合信號(串擾信號)。如下圖中較大的尖峰信號。這些信號還包括插頭座上的信號針之間的串擾信號以及電纜中信號之間的串擾。

決定因素:tr與tf值、線寬、線間距、(基材)介質的厚度、介質的介電常數、平行線長、重疊線長、插頭座信號針地針比、電纜信號線地線比。

6、 反射噪聲

如果IC之間的互連線比較長 (復雜系統往往是這樣) ,線的特性阻抗又不均勻,或者終端沒有匹配,會引起反射,如果始端也不匹配, 則會來回 反射而造成振鈴。 如下圖所示:

決定因素:特性阻抗、匹配方式、失配大小

終端反射系數、始端反射系數、線長

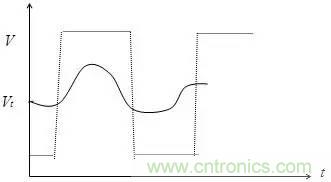

7、邊沿畸變

如果信號頻率升高到一定程度,也就是器件工作頻率達到一定的高度極限,而且印制導線又較長或者負載電容較大時, tr ≥tw上升時間等于或大于脈沖寬度,信號畸變到沒有高低電平平頂或者遠離平頂。如下圖所示(實線):

舉例“仿真或示波器實測”均可驗證。

決定因素:線寬、線長、基材介質厚度、介質介電常數、負載數、工作頻率(脈寬)、tr數字信號的變化。討論了上面七條,可見其畸變不容忽視。如果任其自流,不嚴加限制,造出來的系統不可能穩定、可靠的工作。

(來源:21ic中國電子網)

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理。