【導讀】下一代航天和國防以及測試和測量系統(tǒng)帶寬從10s到100s MHz橫跨到GHz的瞬時帶寬。相控陣雷達、5G無線測試系統(tǒng)、電子戰(zhàn)以及數(shù)字示波器的發(fā)展趨勢正在推動業(yè)內向更高帶寬發(fā)展,并且大幅增加系統(tǒng)中的通道數(shù)量。

這些趨勢使包括數(shù)據轉換器、時鐘和電源等組件的信號鏈設計變得復雜化。選擇合適的數(shù)據轉換器、同步多個通道以及優(yōu)化電源,對于在多個通道上實現(xiàn)必要的帶寬至關重要。

選擇適合的數(shù)據轉換器

每個系統(tǒng)架構都是從對系統(tǒng)性能影響最大的器件開始;在寬帶系統(tǒng)中,最先開始的就是數(shù)據轉換器。選擇哪一款數(shù)據轉換器取決于您對以下問題的回答:

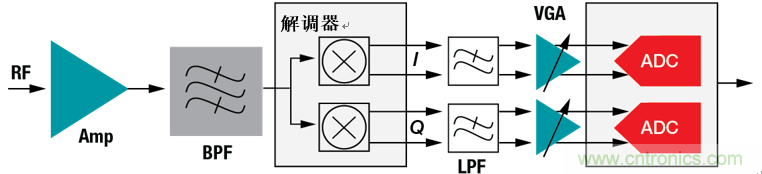

您是否會使用零中頻(IF)/復數(shù)混頻器架構(如圖1所示)?

● 優(yōu)勢:模數(shù)轉換器(ADC)的輸入帶寬和采樣率低于其他架構,由此可簡化或消除濾波。

● 劣勢:對于I和Q路徑,每個天線元件需要兩個ADC通道,且混頻器圖像可能會降低系統(tǒng)性能。

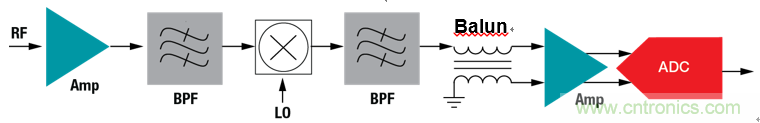

您是否會使用外差法(如圖2所示)?

● 優(yōu)勢:您只需要一個數(shù)據轉換器通道,且ADC輸入帶寬低于射頻(RF)采樣。

● 劣勢:需要一個或多個混頻器,信號圖像和產生的諧波會使濾波復雜化;很難調整響應頻率;必須移動本地振蕩器(LO)。

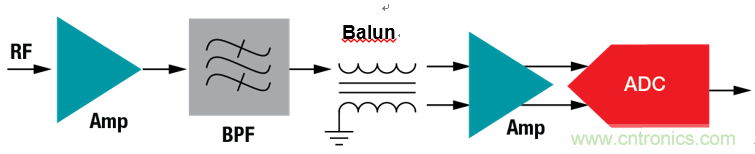

您是否會使用直接射頻采樣(如圖3所示)?

● 優(yōu)勢:由于信號鏈簡化,不再需要混頻器;且使用數(shù)字下變頻器(DDC)和數(shù)控振蕩器(NCO)可以很輕松以數(shù)字方式調整頻率。

● 劣勢:最高信號頻率必須在ADC的輸入帶寬內;需要進行頻率規(guī)劃以實現(xiàn)最高性能。

圖1:“典型的復數(shù)混頻器架構”

圖2:典型的外差架構

圖3:典型的射頻采樣架構

您需要測量的最寬帶寬信號是什么?

● 數(shù)據轉換器的采樣率至少應為直接采樣信號瞬時帶寬的2.5倍,或是零中頻的1.25倍。

● 為獲得最佳性能,約為瞬時帶寬10倍的采樣率將使您更輕松避免信號諧波和雜散。

TI的射頻采樣頻率規(guī)劃器、模擬濾波器和DDC Excel計算器可以滿足頻率規(guī)劃和濾波要求,并向您展示信號的復雜數(shù)字抽取效果。

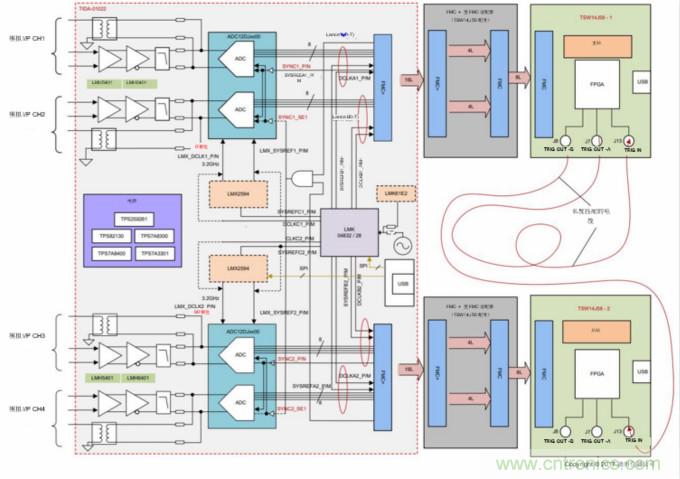

如前所述,寬帶系統(tǒng)需要高采樣率轉換器。例如,信號帶寬為1 GHz的射頻采樣系統(tǒng)可以從帶~10-GSPS轉換速度的數(shù)據轉換器中受益,從而避免信號諧波。目前,TI最快的轉換器是ADC12DJ3200,它是一種12位ADC,可在雙通道模式下每通道運行3.2 GSPS或在單通道模式下運行6.4 GSPS。但即使在單通道模式下,它也不能滿足所需的10-GSPS速度。為了滿足這一要求,適用于DSO、雷達和5G無線測試系統(tǒng)的靈活3.2GSPS多通道AFE參考設計將兩個ADC12DJ3200組合在一塊板上,如圖4所示。

圖4:多通道AFE參考設計框圖

此參考設計提供了系統(tǒng)靈活性,因為它可以在四通道、3.2-GSPS模式或雙通道、6.4-GSPS模式下運行,或者作為一個單通道以高達12.8 GSPS的速度運行。我們的適用于高速示波器和寬帶數(shù)字轉化器的12.8-GSPS模擬前端參考設計說明了兩個ADC的板載交錯。

現(xiàn)在,隨著我們新的雙通道5.2-GSPS ADC12DJ5200RF的推出,您的下一代設計將具有更高的性能和靈活性。由于ADC12DJ5200RF與ADC12DJ3200兼容引腳,我們很快就可以修改現(xiàn)有的參考設計,且現(xiàn)在可以提供適用于12位數(shù)字轉換器的可擴展20.8GSPS參考設計。在20.8GSPS時,器件的整個8-GHz輸入帶寬可以在單個捕獲中實現(xiàn)數(shù)字化。

設計時鐘架構

選擇數(shù)據轉換器之后,就必須設計一個時鐘架構。為單個數(shù)據轉換器提供時鐘非常簡單,但是許多系統(tǒng),比如我們的交錯設計,需要同時為多個轉換器提供時鐘。例如,大型相控陣系統(tǒng)可以有數(shù)百個或數(shù)千個通道。而TI有多個器件和參考設計來應對此設計挑戰(zhàn)。

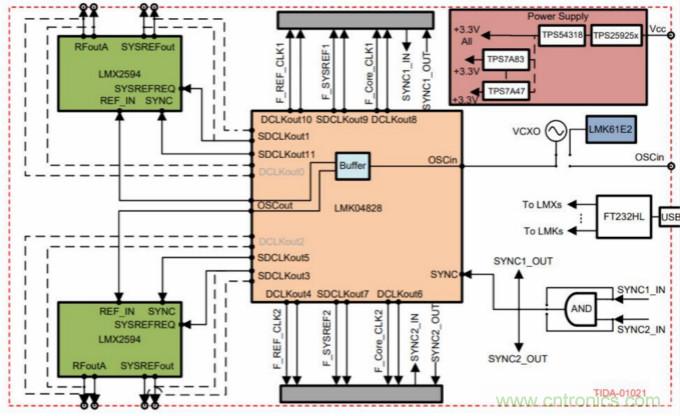

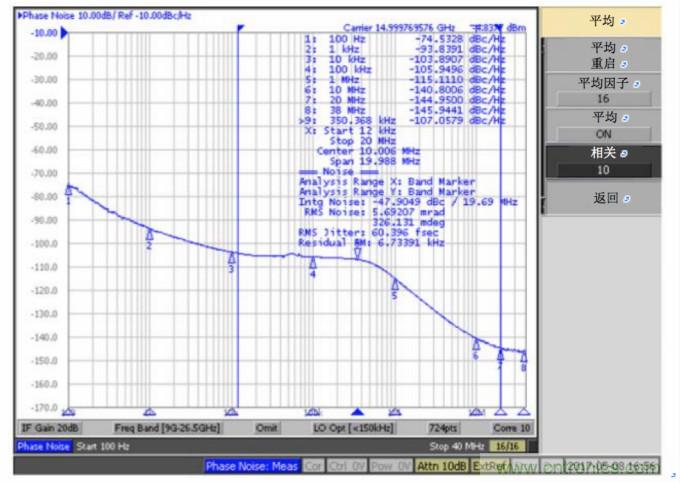

我們的適用于DSO、雷達和5G無線測試儀的多通道JESD204B 15-GHz時鐘參考設計是一個完整的時鐘子系統(tǒng)。此設計(如圖5所示)包含如LMK61E2可編程振蕩器和LMK04828等多個時鐘參考,一個帶有14個獨立時鐘輸出的時鐘分配器件,以及兩個可提供高達15 GHz的超低相位噪聲時鐘的LMX2594鎖相環(huán)/合成器(如圖6所示)。此外,LMX2594還可以為帶JESD204B接口的數(shù)據轉換器生成同步SYSREF時鐘。LMX2594還能夠跨越多個設備同步時鐘的相位。在參考設計中,您可以找到多個頻率下的相位噪聲圖(如圖6所示),并發(fā)現(xiàn)通道到通道偏斜的測量值小于10 ps。

圖5:多通道JESD204B 15-GHz時鐘框圖

圖6:15 GHz時的LMX2594相位噪聲

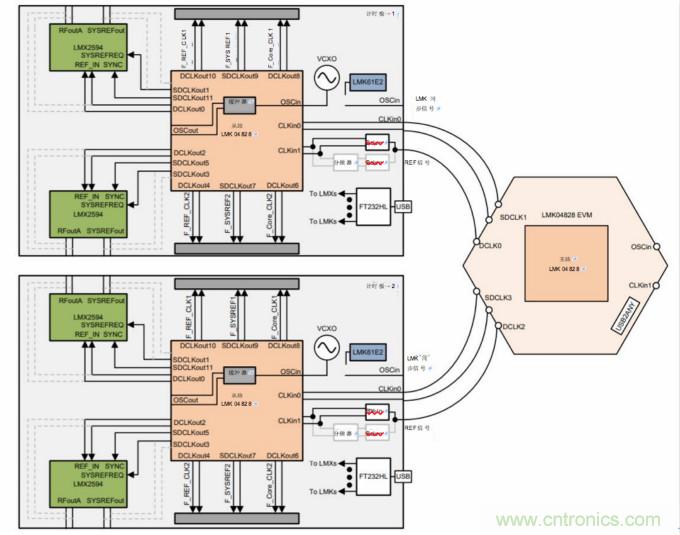

根據配置,該電路板最多支持兩個數(shù)據轉換器和兩個現(xiàn)場可編程門陣列(FPGAs),且可輕松適應多達六個轉換器和一個FPGA的時鐘。然而,許多系統(tǒng)需要更多的通道。對于這類情況,我們的適用于雷達和5G無線測試儀的高通道數(shù)JESD204B時鐘生成參考設計和適用于雷達和5G無線測試儀的高通道數(shù)JESD204B菊鏈時鐘參考設計能夠在樹形結構(如圖7所示)或菊花鏈配置中運行時鐘。您可以使用這些方法擴展到數(shù)千個通道,同時對系統(tǒng)性能的影響降至最低。

圖7:JESD204B時鐘生成參考設計樹形結構框圖

電源設計

一旦時鐘架構確定,那么下一個挑戰(zhàn)就是電源設計。由于數(shù)據轉換器和時鐘對DC/DC轉換器的開關噪聲敏感,所以大多數(shù)電源設計人員都會采用帶低噪聲、低壓差穩(wěn)壓器的DC/DC轉換器(LDO)。然而,經過精心布局和過濾,在許多電源上經常不需要LDO。

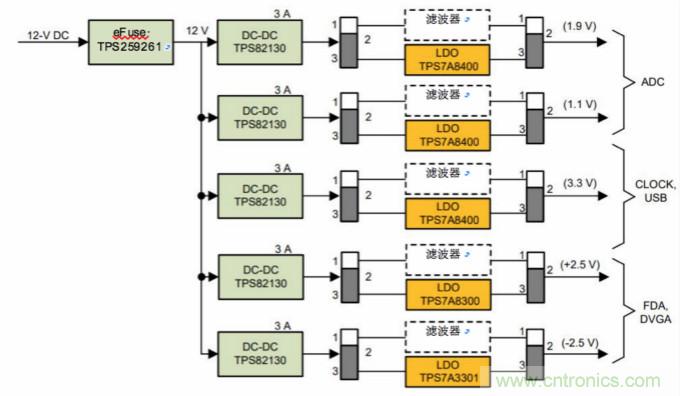

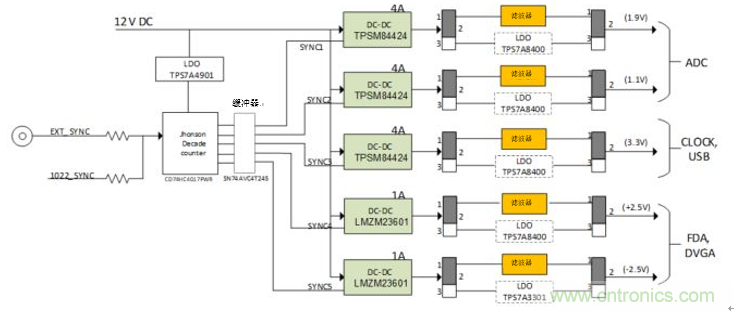

前面提到的3.2-GSPS多通道模擬前端參考設計具有一個完整電源,包括DC/DC穩(wěn)壓器和LDO,如圖8所示。此設計上的LDO可以用濾波器繞過,以測試哪些電源對開關噪聲最敏感。我們的測試證實,繞過LDO時不會對設計的性能產生任何影響,也表明了電源效率增高的額外好處。

圖8:3.2-GSPS多通道AFE參考設計電源框圖

該電路板包含一系列沿頂部的排針引腳,這些排針引腳支持新的設計繞過板載電源解決方案,例如我們的可最大限度提高12.8GSPS數(shù)據采集系統(tǒng)性能的低噪聲電源參考設計(如圖9所示),能夠同步所有DC/DC穩(wěn)壓器與主時鐘,從而更容易濾除轉換器開關噪聲。此外,您可以將時鐘的相位移到每個轉換器,以便所有轉換器不會同時切換,從而降低總開關能量。最后,參考設計上的DC/DC轉換器更加高效,降低了電路板上的總功耗。與最初設計一樣,LDO仍然可以被繞過。

圖9:低噪聲電源參考設計框圖

選擇合適的數(shù)據轉換器只是您面臨的挑戰(zhàn)之一。一旦做出選擇,必須選擇最好的時鐘和電源設計,以免降低昂貴的數(shù)據轉換器的性能。

推薦閱讀: