【導讀】防輻射低壓降穩壓器(LDO)是許多空間級子系統的重要電源組件,包括現場可編程門陣列(FPGA),數據轉換器和模擬電路。LDO有助于確保其性能取決于干凈輸入的組件的穩定,低噪聲和低紋波供電。

防輻射低壓降穩壓器(LDO)是許多空間級子系統的重要電源組件,包括現場可編程門陣列(FPGA),數據轉換器和模擬電路。LDO有助于確保其性能取決于干凈輸入的組件的穩定,低噪聲和低紋波供電。

但是,由于市場上有如此眾多的LDO,您如何為子系統選擇正確的輻射硬化設備?讓我們看一些設計規范和設備功能,以幫助您做出此決定。

空間級LDO的壓差電壓

LDO的壓差是輸入和輸出電壓之間的電壓差,此時LDO停止調節輸出電壓。壓差電壓規格越小,可以使用的工作電壓差就越低,從而導致更少的功率和熱耗散以及本質上更高的最大效率。如公式1所示,這些好處在更高的電流下變得更加顯著:

LDO功耗=(V IN -V OUT)xI OUT (1)

在經過防輻射處理的市場中,很難找到真正的低壓差穩壓器,它們在輻射,溫度和老化方面均具有出色的性能。TI的輻射硬化LDO TPS7H1101A-SP就是一個例子,在3 A時提供210 mV的典型壓降(Vdo)–目前,這是市場上最低的。如果您有可用的5V,3.3V,2.5V或1.8V標準電源軌,則此LDO可以將輸出電壓調節至低至0.8V,以提供任何所需的電壓以及一個或多個空間所需的電流級的模數轉換器(ADC)或時鐘。

空間LDO的噪聲性能

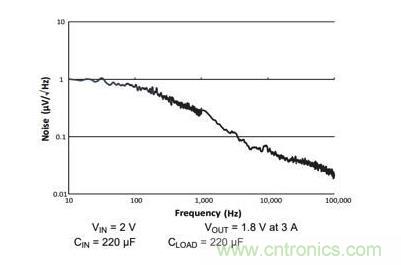

隨著衛星在太空中使用10年或更長時間,利用機載集成電路發揮出最佳性能有助于確保設計壽命。為了為高性能時鐘,數據轉換器,數字信號處理器或模擬組件提供干凈的低噪聲軌,LDO電路產生的內部噪聲必須降至最低。由于不容易過濾內部產生的1 / f噪聲,因此請尋找具有固有低噪聲特性的LDO。低頻噪聲通常是最大的,并且最難以濾除。所述TPS7H1101A-SP提供了最低的1 / f噪聲電平之一,約有1μV/峰值√以10Hz赫茲。關于整個頻率的RMS噪聲,請參見下面的圖1。

圖1:TPS7H1101A-SP噪聲

空間LDO的PSRR

電源抑制比(PSRR)衡量LDO清除或抑制來自上游其他組件的噪聲的能力。對于高端ADC,輸入電源噪聲要求繼續趨于嚴格,以最大程度地降低誤碼率。在較高的頻率下,鑒于控制環路的特性,很難獲得較高的PSRR。通常,設計人員需要使用外部組件來過濾噪聲,以達到可接受的有效PSRR,這會增加解決方案的尺寸-對于太空應用而言,這是一個明顯的問題,因為太空應用的尺寸和重量直接與衛星發射成本相關。PSRR在上游電源的開關頻率上最為重要(因為此頻率上存在電壓紋波)。另外,由于開關諧波,在該頻率以上,PSRR非常重要。如果您正在尋找良好的PSRR,TPS7A4501-SP LDO在100 kHz時提供超過45 dB的PSRR。

其他重要的LDO功能

除了壓差,PSRR和噪聲之外,讓我們看一下可以與防輻射LDO的性能集成在一起的幾個智能功能。

●使能夠。在太空中,太陽能板只能提供一定量的電力,許多功能都需要從中運行。通過啟用功能,您可以指定在任何給定時間應打開還是關閉LDO,并證明對于節省電源預算的總體成本至關重要。使能引腳對于上電排序也很重要,這在新一代FPGA中的需求越來越大。

●慢啟動。電壓上升太快會導致電流過沖或過大的峰值浪涌電流,從而損壞下游組件,如FPGA或ADC。軟啟動功能可調節啟動時輸出電壓的上升速度。軟啟動還通過防止上游電源汲取過電流來防止電壓下降,這是不可接受的。

●輸出電壓精度。通常,諸如Xilinx KU060之類的新型空間級FPGA在每個電源軌上都具有嚴格的輸入電壓容限要求,以實現其最佳性能。為了確保您的設計滿足輻射暴露和結束時的生活條件,看起來像設備嚴格的精度要求TPS7H1101A-SP,這是對KU060開發板。

●大小。除了采用小型,易于布局的封裝外,其他減小解決方案尺寸的方法還包括限制LDO的外部組件數量;具有更多的集成功能,更好的PSRR和噪聲規范;在單事件效應下具有更可靠的輻射性能。無論是封裝尺寸,布局還是解決方案尺寸,TI的TPS7A4501-SP都是業界最小的輻射硬化LDO之一。

結論

有這么多的可用選項,可能很難選擇正確的LDO。考慮哪些功能最重要。例如,如果您的應用程序為高端FPGA或高速數據轉換器供電,則輸出電壓精度,參考精度,PSRR和噪聲等功能可能是優先考慮的事情。但是,如果您正在設計性能低下的模擬電路或使用對容忍度要求不是那么嚴格的較舊的FPGA,則擁有最小尺寸,最低成本的解決方案同時保留足夠的性能可能是更好的選擇。

(來源:TI,作者:Sree Alvarado)

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請電話或者郵箱聯系小編進行侵刪。