鎖相環(PLL)電路存在于各種高頻應用中,從簡單的時鐘凈化電路到用于高性能無線電通信鏈路的本振(LO),以及矢量網絡分析儀(VNA)中的超快開關頻率合成器。

今天,我們就參考上述各種應用來介紹PLL電路的一些構建模塊,以指導器件選擇和每種不同應用內部的權衡考慮,這對新手和PLL專家均有幫助。本文參考 ADI 的 ADF4xxx 和 HMCxxx 系列PLL和壓控振蕩器 (VCO),并使用 ADIsimPLL(ADI 內部PLL電路仿真器)來演示不同電路性能參數。詳細閱讀>>

干貨

干貨

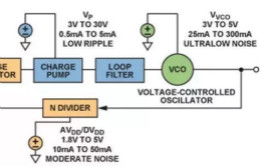

PLL(Phase Locked Loop): 為鎖相回路或鎖相環,用來統一整合時鐘信號,使高頻器件正常工作,如內存的存取資料等。PLL用于振蕩器中的反饋技術。 許多電子設備要正常工作,通常需要外部的輸入信號與內部的振蕩信號同步。一般的晶振由于工藝與成本原因,做不到很高的頻率,而在需要高頻應用時,由相應的器件VCO,實現轉成高頻,但并不穩定,故利用鎖相環路就可以實現穩定且高頻的時鐘信號。

?

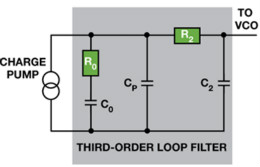

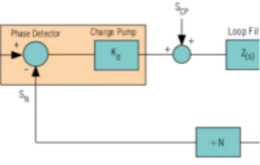

如參考文獻中所描述,可采用標準過程來確定鎖相環(PLL)中二階環路濾波器的R0、C0 和CP 數值。它采用開環帶寬(ω0)和相位裕量(?M)作為設計參數,并可擴展至三階環路濾波器,從而確定R2 和C2(圖1)。該過程可直接解出CP,然后推導出其余數值。詳細閱讀>>

?

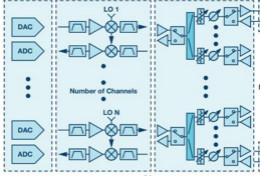

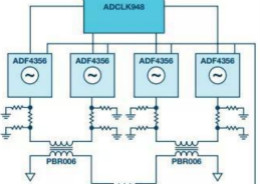

對于數字波束成形相控陣,要生成本地振蕩器(LO) ,通常會考慮的實現方法是向分布于天線陣列中的一系列鎖相環分配常用基準頻率。對于這些分布式鎖相環,目前文獻中還沒有充分記錄用于評估組合相位噪聲性能的方法。詳細閱讀>>

?

隨著人們對通信系統的頻率帶寬、吞吐量和動態范圍的需求日益提高,同時還要求毫米波5G使用更高的天線頻率,因此對于通信系統或混合信號系統中使用的本地振蕩器(LO)或時鐘的質量也分別提出了更高的要求。詳細閱讀>>

?

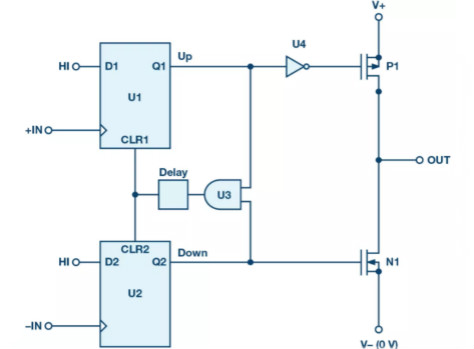

顧名思義,鎖相環(PLL)使用鑒相器比較反饋信號與參考信號,將兩個信號的相位鎖定在一起。雖然這種特性有許多用武之地,但是PLL如今最常用于頻率合成,通常充當上變頻器/下變頻器中的本振(LO),或者充當高速模數轉換器(ADC)或數模轉換器(DAC)的時鐘。詳細閱讀>>

?

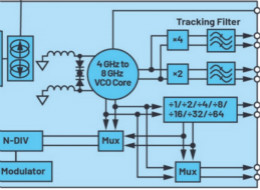

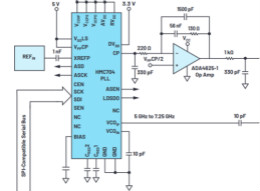

RF 和微波儀器(比如信號和網絡分析儀)需使用寬帶掃頻信號來進行大多數基本測量。但寬帶壓控振蕩器(VCO)通常會因最大限度擴大調諧范圍所需的低 Q 和高 KVCO(VCO 的調諧靈敏度,單位:MHz/V)而具有最糟糕的相位噪聲。釔鐵石榴石(YIG)調諧振蕩器憑借良好的寬帶相位噪聲性能和一個倍頻程頻率調諧范圍巧妙地解決了該問題,但體積可能較大且費用昂貴...詳細閱讀>>

?

鎖相環(PLL)是一種反饋系統,其中電壓控制振蕩器(VCO)和相位比較器相互連接,使得振蕩器可以相對于參考信號維持恒定的相位角度。在使用PLL的過程中您都遇到過哪些問題呢?詳細閱讀>>

基礎知識

基礎知識

?

鎖相環(PLL)是現代通信系統的基本構建模塊,通常用在無線電接收機或發射機中,主要提供“本振”(LO)功能;也可用于時鐘信號分配和降噪,而且越來越多地用作高采樣速率模數或數模轉換的時鐘源。詳細閱讀>>

?

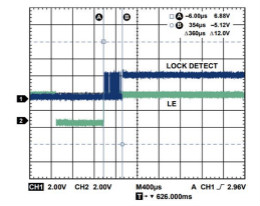

利用手動頻段選擇,鎖定時間可從典型值 4.5 ms 縮短到典型值 360 μs。本文以高度集成的解調器和頻率合成器 ADRF6820 為例,告訴大家如何手動選擇頻段以縮短PLL鎖定時間。詳細閱讀>>

?

多年來,微波頻率生成使工程師面臨嚴峻的挑戰,不僅需要對模擬、數字、射頻(RF)和微波電子有深入的了解,尤其是鎖相環(PLL)和壓控振蕩器(VCO)集成電路組件方面,還需要具備可調濾波、寬帶放大以及增益均衡等專業知識。詳細閱讀>>

鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。因鎖相環可以實現輸出信號頻率對輸入信號頻率的自動跟蹤,所以鎖相環通常用于閉環跟蹤電路。鎖相環在工作的過程中,當輸出信號的頻率與輸入信號的頻率相等時,輸出電壓與輸入電壓保持固定的相位差值,即輸出電壓與輸入電壓的相位被鎖住,這就是鎖相環名稱的由來。

關于我們 | About Us | 聯系我們 | Contact Us | 隱私政策 | 版權申明 | 投稿信箱 | 網站地圖

Copyright ? hdh-sz.com? All Rights Reserved

電子元件技術網 版權所有 ??粵ICP備10202284號??粵ICP證B2-20090022

未經版權所有人明確的書面許可,不得以任何方式或媒體翻印或轉載本網站的部分或全部內容。