【導讀】在雷達應用中,相位噪聲是要求高雜波衰減的系統的關鍵性能指標。相位噪聲是所有無線電系統都會關心的問題,但是雷達相比通信系統來說特別要求非常靠近載波頻率的頻偏位置的相位噪聲性能。

這些高性能系統中的系統設計人員將選擇超低相位噪聲振蕩器,并且從噪聲角度來講,信號鏈的目標就是使振蕩器相位噪聲曲線的惡化最小。這就要求對信號鏈上的各種元器件做殘余或加性的相位噪聲測量。

最近發布的高速數模轉換器(DAC)產品對于頻率轉換階段需要的任何LO的波形生成和頻率創建都非常有吸引力。然而,雷達目標會挑戰DAC相位噪聲的性能。

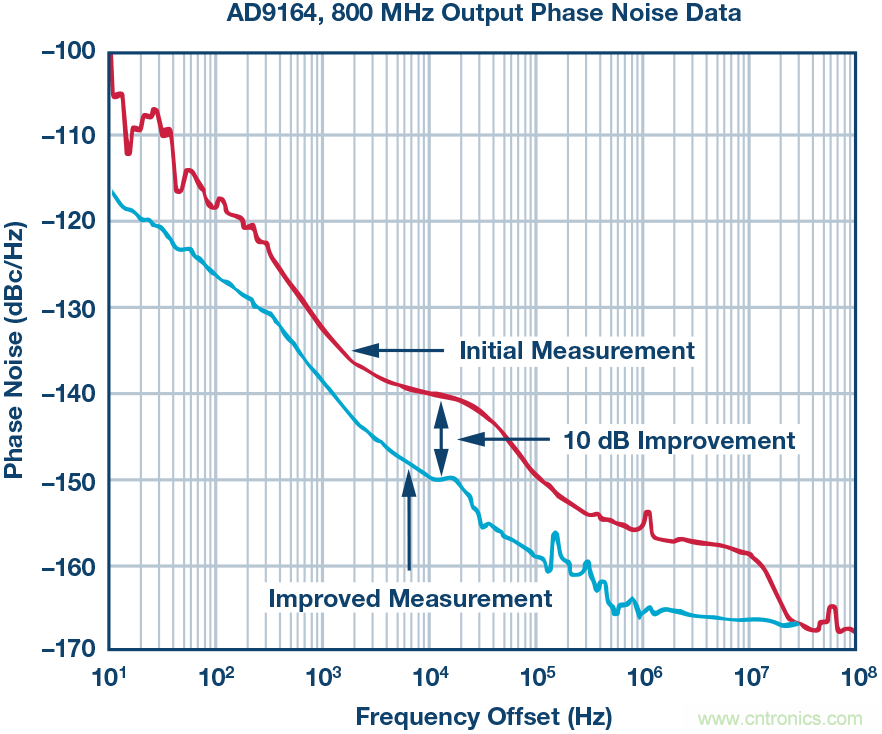

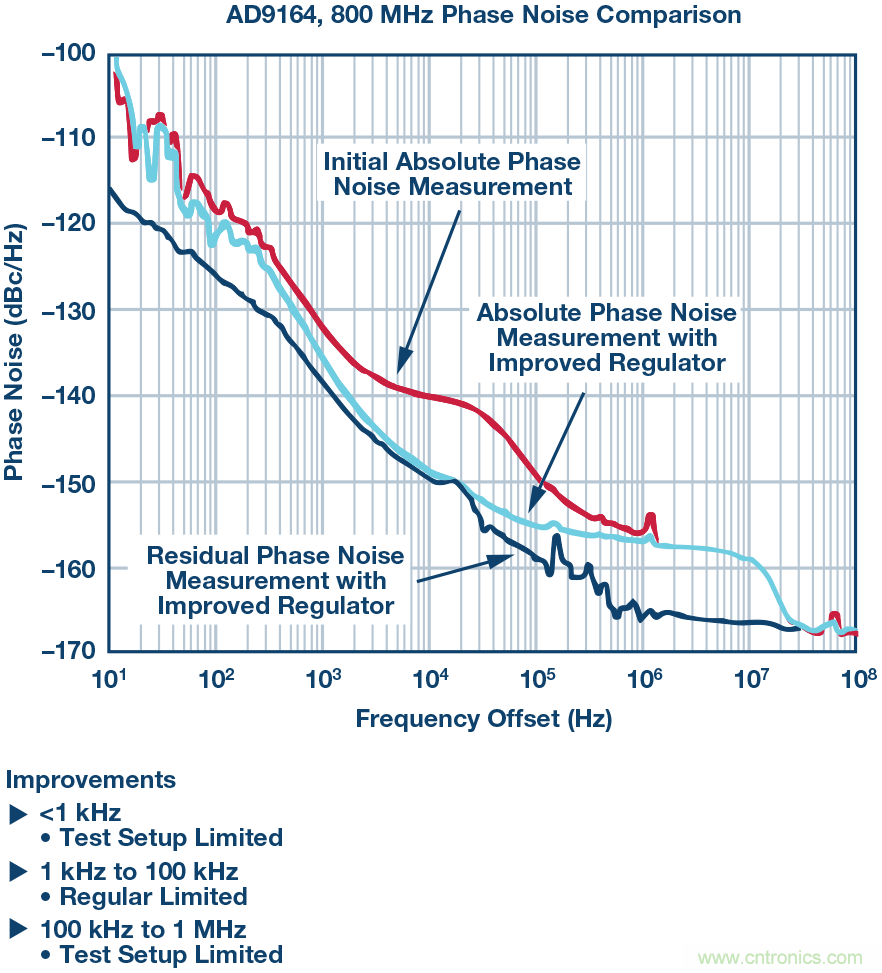

圖1. AD9164相位噪聲的改進。

在本文中,我們將展示AD9164 DAC在10KHz 頻偏處超過10dB的改進 的測量結果。改進如圖1所示,并且我們將會討論如何通過結合電源穩壓器選擇和測試設置改進來達到這一結果。

相位噪聲定義

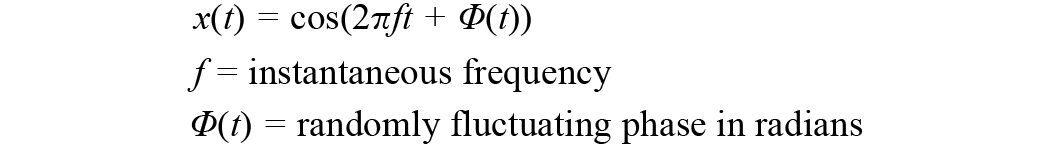

相位噪聲是周期信號過零點偏差的測量。考慮有相位波動的余弦波

相位噪聲可以通過相位變化的功率譜密度來確定

就線性而言,單邊相位噪聲定義為

相位噪聲 通常以10log(L(f))的dBc/Hz為單位來表示。然后可以將相位噪聲數據繪制到相對RF載波的偏移頻率中。

圖2. 相位噪聲繪圖方法。

相位噪聲進一步的重要定義就是絕對相位噪聲和殘余相位噪聲。絕對相位噪聲是系統中測量的總相位噪聲。殘余相位噪聲是測試設備的加性相位噪聲。這種區別在測試設置和確定系統中元件級別相位噪聲貢獻的過程中至關重要。

DAC/DDS相位噪聲測量方法

本部分圖表顯示DDS相位噪聲測試設置。對于DAC相位噪聲測量,可以設想將DAC作為直接數字頻率合成器(DDS)子系統的一部分。DDS是通過將與DAC通信的單片IC或FPGA或ASIC中的數字正弦波模式送給DAC來實現。在現代DDS設計中,數字相位誤差可以遠低于DAC誤差,而且DDS相位噪聲測量通常受限于DAC的性能。

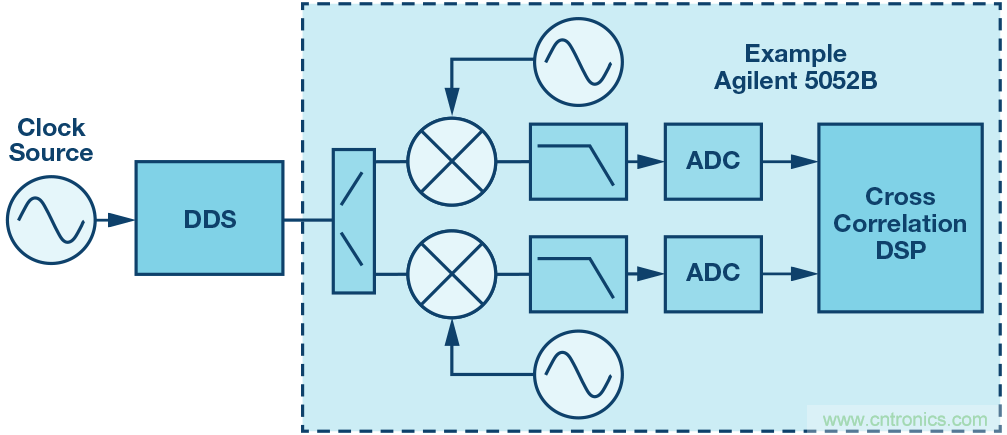

最簡單和最常見的測試設置如圖3所示。一個時鐘源用于DDS并且DDS的輸出饋入到一個互相關類型的相位噪聲分析儀 。由于只需要一個DDS,所以很容易實現。然而,在這樣的測試設置下,沒有辦法提取振蕩器的貢獻以便僅僅顯示DDS的相位噪聲。

圖3. 絕對相位噪聲DDS測試設置包含DAC和振蕩器噪聲。

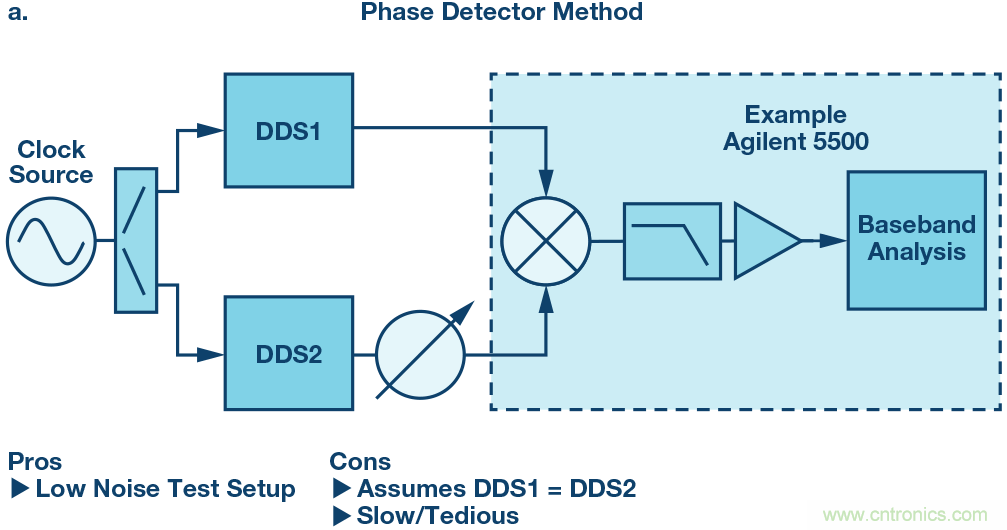

圖4顯示了兩種常用的方法用來從測量中去除振蕩器的相位噪聲 ,提供殘余噪聲測量。這些測量方法的缺點在于,在測試設置中需要額外的DAC。但是,優點是可以應用于系統級分析預算,作為DAC相位噪聲貢獻的一種非常好的指標。

圖4a. 使用鑒相器方法的DDS殘余相位噪聲測量。

圖4a顯示的是鑒相器方法。這種情況下,使用兩個DAC,將兩個DUT都下變頻至DC,可以減去振蕩器的貢獻。

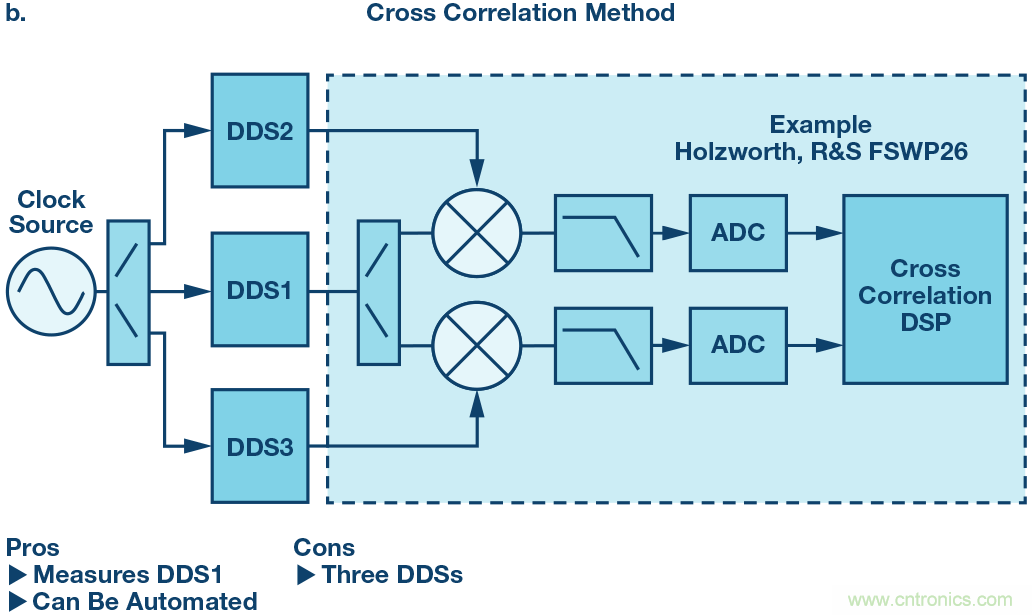

圖4b. 使用互相關方法測量DDS殘余相位噪聲。

圖4b顯示的是使用互相關相位噪聲分析的方法。這種情況下,DDS2和DDS3可以用于將時鐘貢獻轉換到測量的LO端口,在互相關算法中去除它們的貢獻,并在測量中獲取DDS1殘余相位噪聲。

電源噪聲貢獻

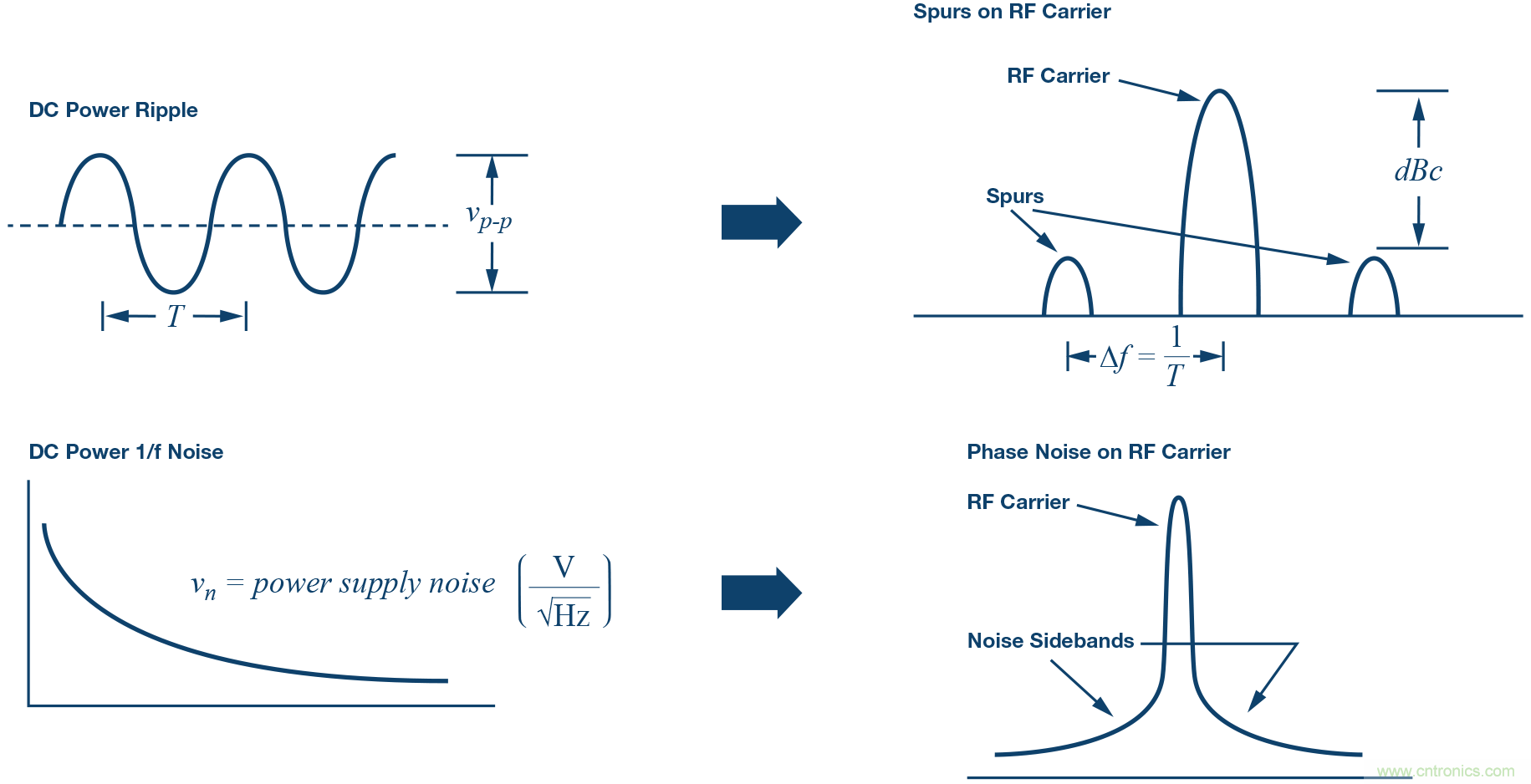

在低噪聲模擬和RF設計中,電源噪聲是公認需要考慮的因素。電源紋波會周期性的調制到RF載波并在RF載波的頻偏等于紋波頻率的地方產生雜散。穩壓器1/f噪聲也會調制到RF載波中,并體現在相位噪聲曲線中。圖5顯示了這些原理。

圖5. 電源缺陷調制到RF載波上。

測量結果

在研究DAC真正的相位噪聲性能的過程中,需要同時考慮測試設置和穩壓器的噪聲性能。

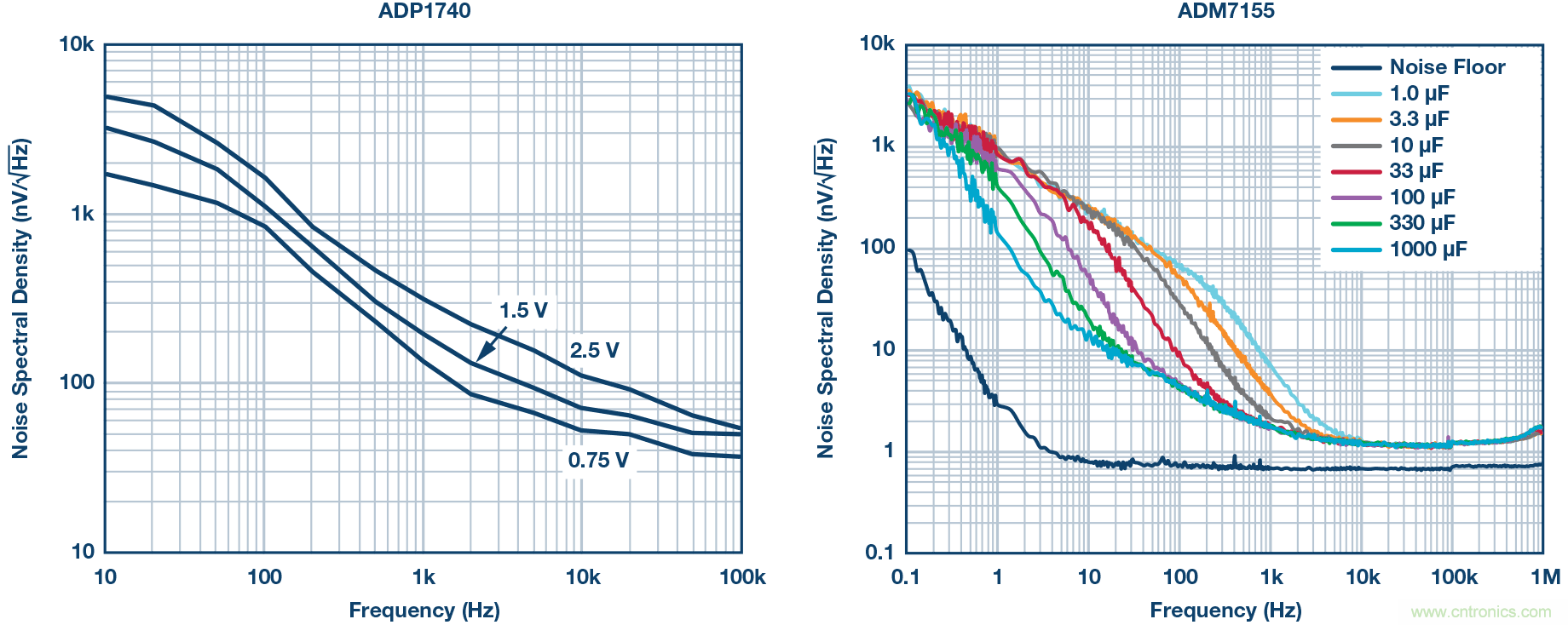

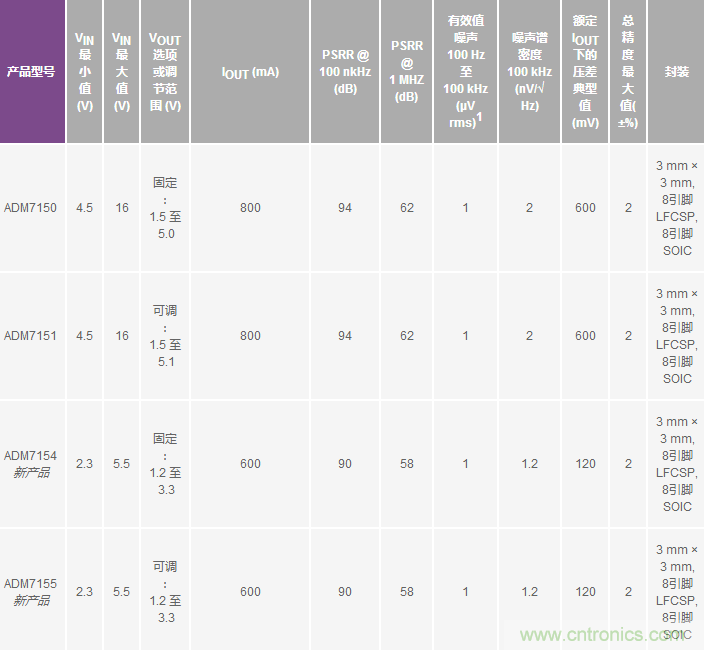

DAC初始評估板包含 ADP1740 穩壓器用于給模擬和時鐘提供電壓。 將噪聲譜密度與最近發布的超低噪聲穩壓器和所選的ADM7155進行對比。圖6如產品數據手冊所示顯示了這些噪聲密度的對比情況。電源修改僅將ADM7155用于AD9164時鐘(數據手冊引腳VDD12_CLK)和模擬電壓(數據手冊引腳VDD12A)。

圖6. 穩壓器噪聲密度比較。注意Y軸單位——ADM7155提高了一個數量級。

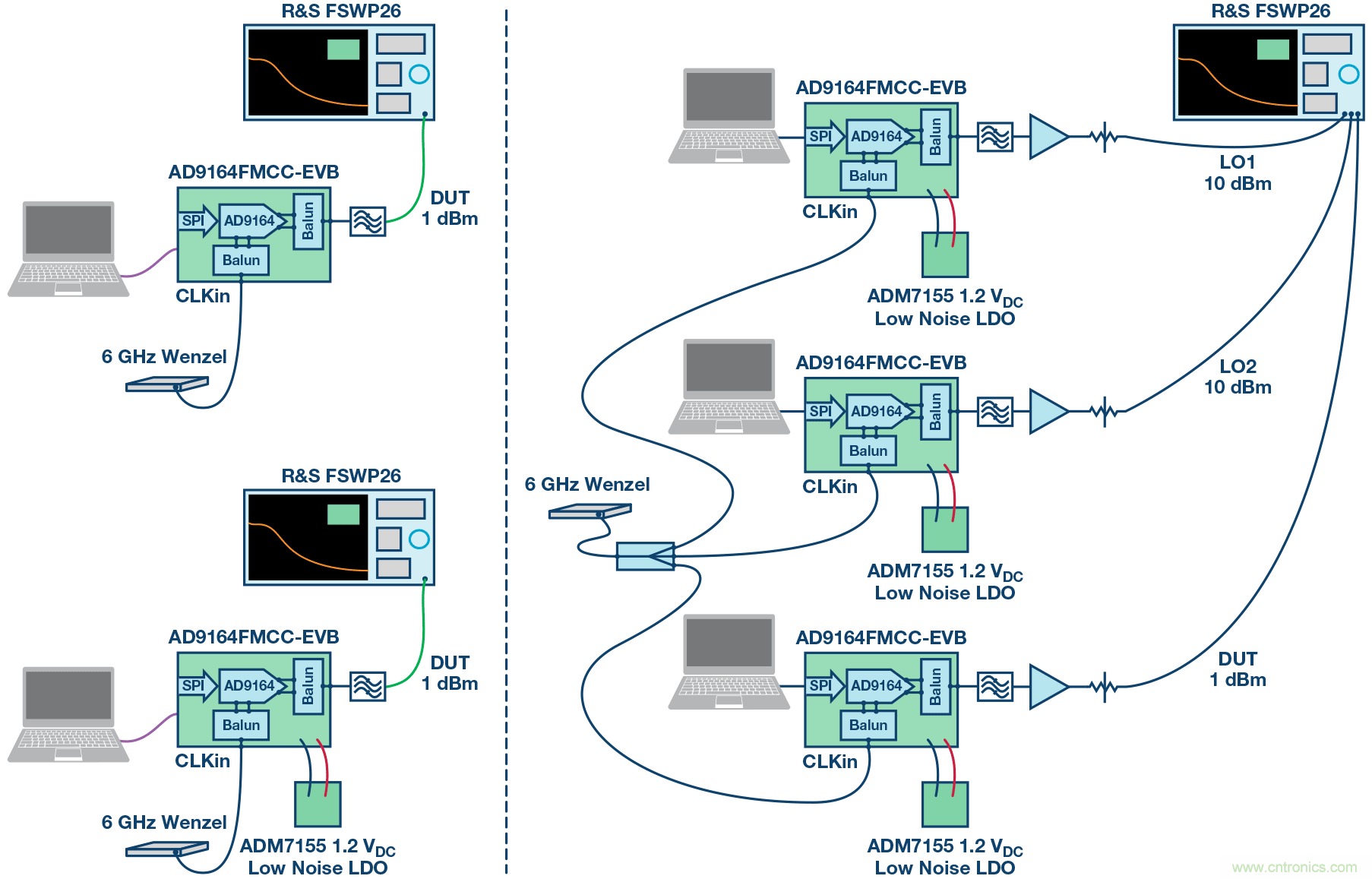

接下來,考慮殘余相位噪聲的測試設置選項。由于實用性和方便性,自帶互相關方法的Rohde and Schwarz FSWP成為首選。使用的測試設置如圖7所示。

圖7. AD9164相位噪聲測量的測試設置。

圖8. AD9164 800 MHz output phase noise comparisons.

圖8顯示了三種情況的測量結果。紅色曲線顯示了初始評估板的絕對相位噪聲測量結果。淺藍色曲線也是一種絕對測量結果,但提升了穩壓器性能。深藍色曲線是殘余相位噪聲測量結果,也提升了穩壓器性能。

測量結果指出了在初始研究中并不明顯的三種常規的限制區間。低于1 kHz的頻率受限于時鐘源近載波噪聲。1 kHz至100 kHz的頻率受限于穩壓器選擇。高于100 kHz的頻率受限于時鐘源。由于使用的時鐘是用晶體振蕩器倍頻產生的6GHz,滾降來自于倍頻電路中的RF濾波器,因此高于10 MHz的急劇下降來自于時鐘源。

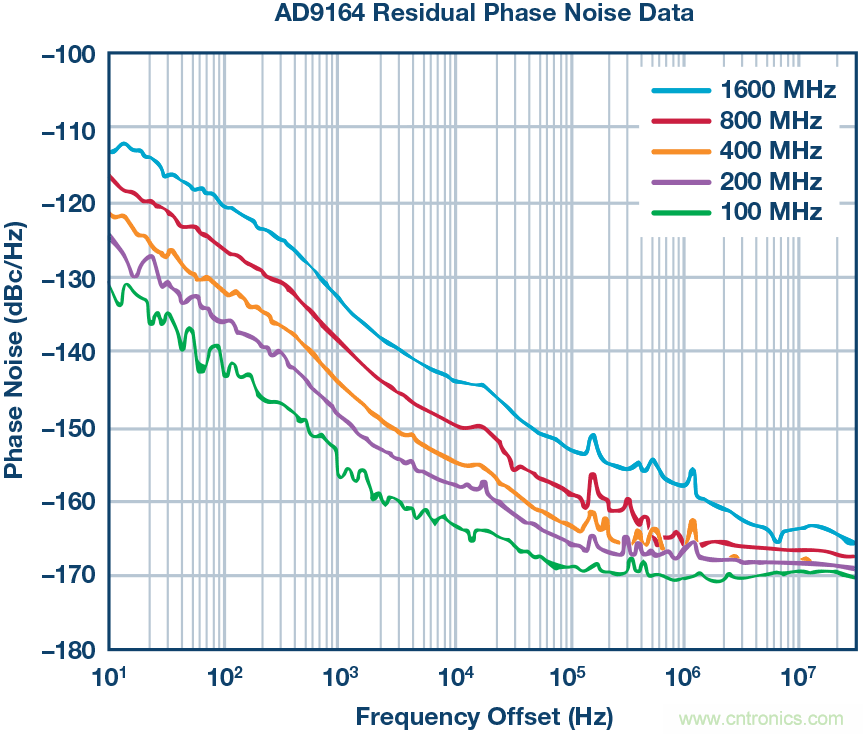

其他的一些DAC頻率也使用了提升穩壓器性能的殘余相位噪聲方法進行了測量,圖9中概述了部分。這些改進在幾個評估板上都做了復現,所有的情況都顯示了同樣的改進后的結果。

圖9. 改進了低噪聲穩壓器性能的AD9164殘余相位噪聲測量。

表1. 包含一流的噪聲密度性能的穩壓器系列

1噪聲與固定輸出電壓無關。

超低噪聲穩壓器系列的噪聲密度相似,如表1所示。正如本文所展示的,穩壓器對DAC的相位噪聲影響是值得注意的,超低噪聲穩壓器系列推薦用于任何要求最佳的相位噪聲性能的RF系統中。

結語

相位噪聲基礎定義的復習、絕對和殘余相位噪聲、DAC相位噪聲測量測試設置以及穩壓器噪聲貢獻。

本文演示的DAC相位噪聲性能改進包含殘余相位噪聲測量方法和最佳穩壓器選擇。最終結果是,通過ADI公司的低噪聲穩壓器系列對模擬電壓和時鐘電壓供電時,AD9164現在可支持超低相位噪聲、基于DDS的應用。

參考電路

Bergeron, Jarrah. “分析及管理電源噪聲和時鐘抖動對高速DAC相位噪聲的影響”,《模擬對話》,第51卷,2017年。

Calosso, Claudio E., Yannick Gruson, and Enrico Rubiola. "DDS中的相位噪 聲和幅度噪聲",IEEE頻率控制專題論文集,2012年。

Jayamohan, Umesh. "為GSPS或RF采樣ADC供電;開關與LDO"。《模擬對話》,第50卷,2016年。

"11729B-1產品筆記,微波振蕩器的相位噪聲特性:鑒相器方法"。 Agilent, May,2007年5月。

Reeder, Rob. "高速ADC的電源設計",ADI公司,2012年。

Walls, Warren F. "交叉相關相位噪聲測量"。IEEE頻率控制專題論文集,1992年。

推薦閱讀: