【導讀】任何高性能模數轉換器(ADC),尤其是射頻采樣ADC,輸入或前端的設計對于實現所需的系統級性能而言很關鍵。很多情況下,射頻采樣ADC可以對幾百MHz的信號帶寬進行數字量化。前端可以是有源(使用放大器)也可以是無源(使用變壓器或巴倫),具體取決于系統要求。無論哪種情況,都必須謹慎選擇元器件,以便實現在目標頻段的最優ADC性能。

射頻采樣ADC采用深亞微米CMOS工藝技術制造,并且半導體器件的物理特性表明較小的晶體管尺寸支持的最大電壓也較低。因此,在數據手冊中規定的出于可靠性原因而不應超出的絕對最大電壓,將當前主流的射頻采樣ADC與之前的老器件相比,可以發現這個電壓值是變小的。

在使用ADC對輸入信號進行數字量化的接收機應用中,系統設計人員必須密切關注絕對最大輸入電壓。該參數直接影響ADC的使用壽命和可靠性。不可靠的ADC可能導致整個無線電系統無法使用,且更換成本也許非常巨大。

為了抵消過壓帶來的風險,射頻采樣ADC集成了可以檢測高電平閾值的電路,允許接收機通過自動增益控制(AGC)環路調節增益來進行補償。但是,如果采用流水線型ADC,則與架構相關的固有延遲可能導致輸入暴露于高電平之下,從而可能損害ADC輸入。本文討論了一種簡單的方法來增強AGC環路,保護ADC。

輸入架構

射頻采樣ADC可采用多種不同的設計,最常見的一種是流水線架構,該架構采用多級級聯,將模擬信號轉換為數字信號。第一級最重要,可以是緩沖或未緩沖級。選擇哪種設計取決于設計要求和性能目標。例如,一個帶緩沖器的ADC通常在頻率范圍內具有更好的SFDR性能,但功耗比不帶緩沖器的ADC更高。

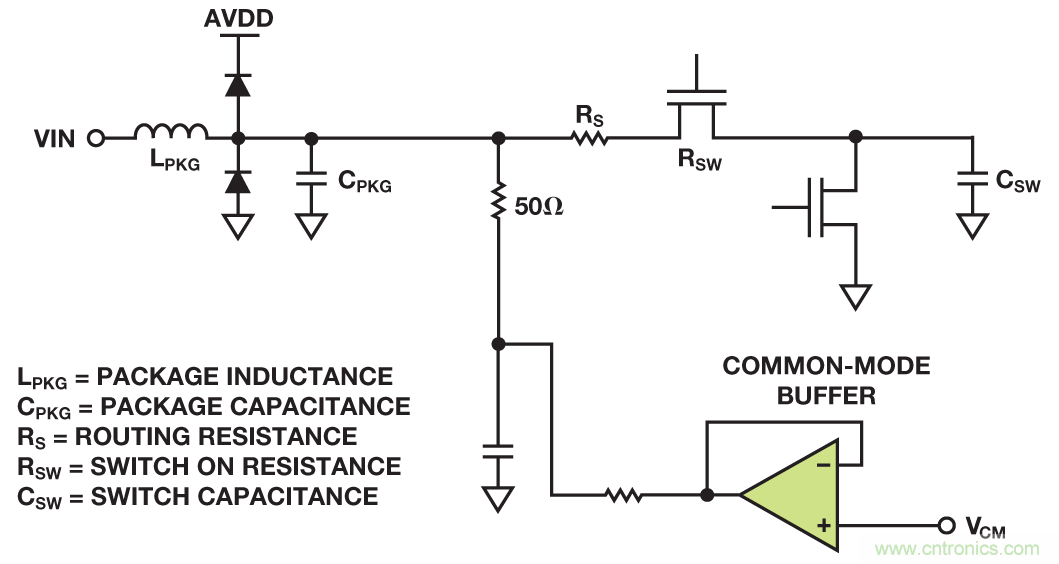

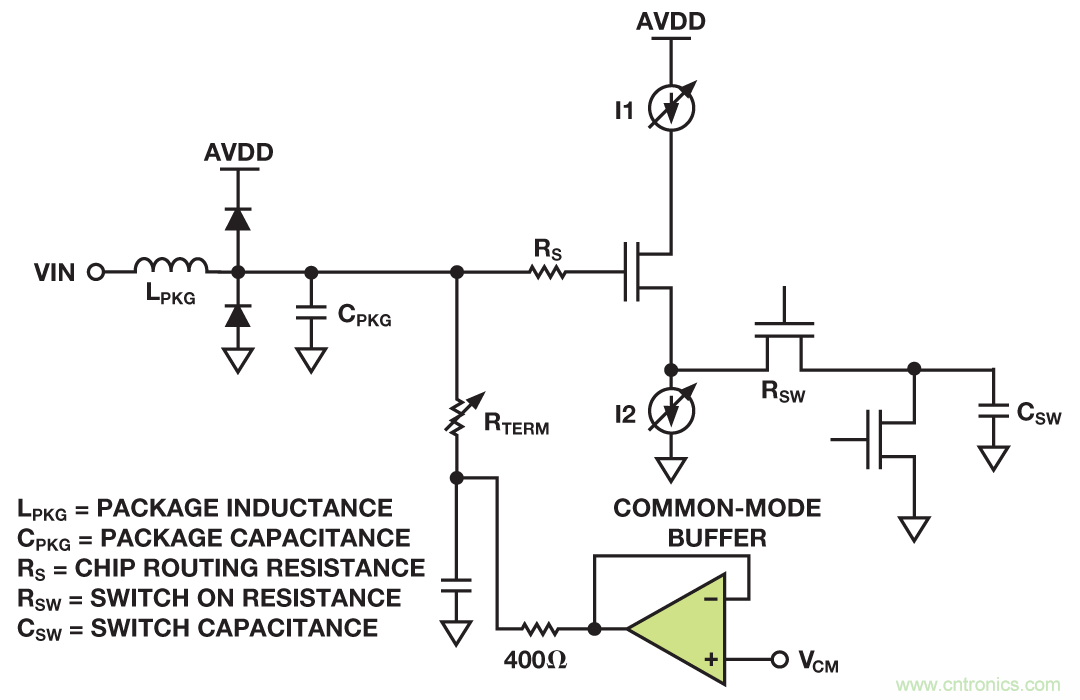

前端設計同樣會根據ADC是否有緩沖級而改變。沒有緩沖器的ADC需要使用額外的串聯電阻來處理輸入電荷反沖,它同樣會改善SFDR性能。圖1和圖2顯示了AD9625未緩沖和AD9680緩沖射頻采樣ADC的等效輸入電路簡化圖。為簡明起見,僅顯示單端輸入。

圖1. 未緩沖射頻采樣ADC輸入的等效電路

圖2. 緩沖射頻采樣ADC輸入的等效電路

無論采用何種架構,ADC輸入端可持續的絕對最大電壓由MOSFET能夠處理的電壓決定。緩沖輸入更復雜,且比未緩沖輸入功耗更大。ADC具有多種不同類型的緩沖器,最常見的一種是源極跟隨器。

故障機制

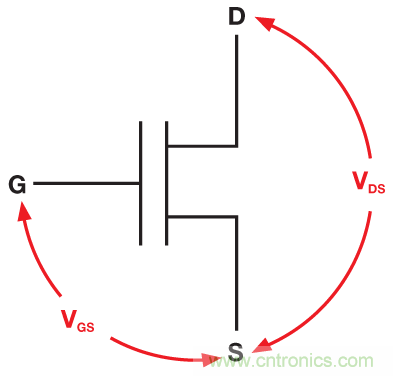

緩沖和未緩沖ADC的故障機制有所不同,但通常是在超出允許的最大柵極-源極電壓(VGS)或漏極-源極電壓(VDS)時發生故障。這些電壓如圖3所示。

圖3. MOS晶體管的關鍵電壓

例如,假設VDS超過允許的最大電壓,則發生VDS擊穿故障,這通常在MOSFET處于關斷狀態且在漏極施加了相對于源極的過量電壓時發生。如果VGS超過允許的最大電壓,則它會導致VGS擊穿(亦稱為氧化層擊穿)。這通常在MOSFET處于導通狀態且在柵極施加了相對于源極的過量電壓時發生。

未緩沖ADC的故障機制

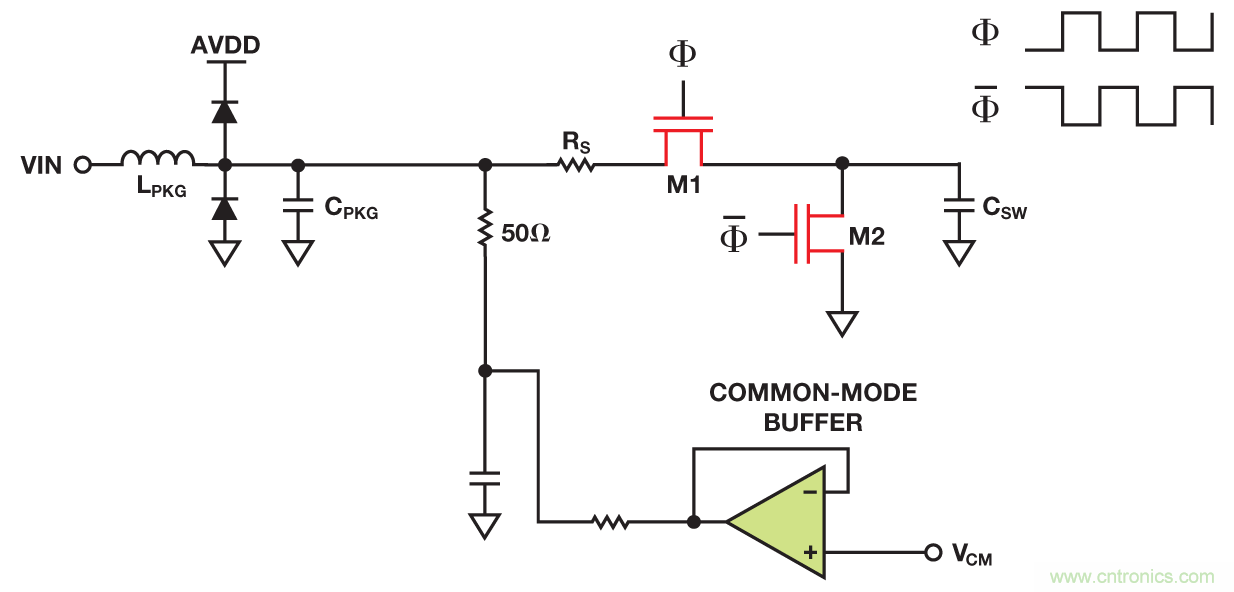

圖4顯示的是一個未緩沖ADC輸入。采樣過程由反相時鐘信號Φ和Φ控制,它們是MOSFET M1的采樣/保持信號以及MOSFET M2的復位信號。M1導通時,M2關斷,且電容CSW跟蹤信號(采樣或跟蹤模式)。當M1關斷時,MDAC中的比較器作出判斷后M2導通,電容CSW復位。這樣可在采樣階段使采樣電容為下一次采樣做好準備。該電路通常工作狀態優良。

但是,高壓輸入使M2暴露在超出其漏源電壓的應力之下。當對輸入高壓進行采樣(M1導通、M2關斷)時,M2會暴露于較大的VDS之下,其在不足采樣時鐘半周期的時間內處于關斷狀態,但哪怕只是瞬時的暴露也會降低電路的可靠性,導致ADC隨時間失效。在復位模式下(M1關斷、M2導通),因M1的漏極上有輸入信號,從而也會暴露于大的VDS電壓。

圖4. 未緩沖ADC輸入的故障模式

緩沖ADC的故障機制

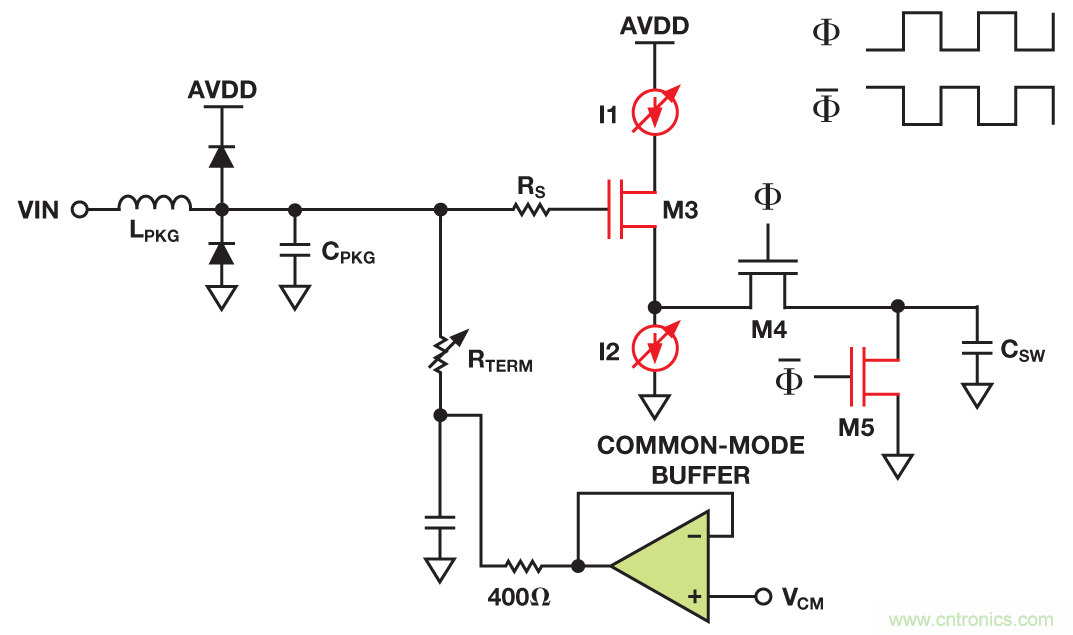

圖5顯示的是一個緩沖ADC輸入。采樣和復位信號適用相同的時鐘方案。無論相位如何,當緩沖器M3柵極暴露于高壓輸入時,產生電流I1以及I2。電流源I1采用PMOS晶體管實現,而I2采用NMOS晶體管實現。M3柵極上的高電壓導致I1和I2 MOSFET產生過大的VDS。此外,M3柵極上的高電壓還可導致氧化層擊穿。

圖5. 緩沖ADC輸入的故障模式

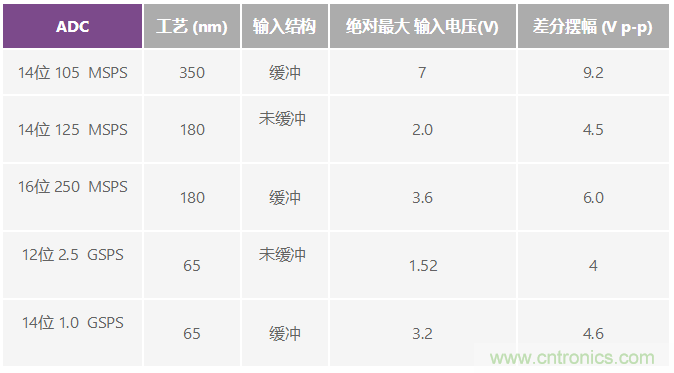

緩沖和未緩沖ADC的擊穿機制有所不同,因此絕對最大輸入電壓同樣有所不同,如表1所以。

表1. 緩沖與未緩沖ADC的絕對最大值規格

ADC Input Protection Using a TVS Diode

ADC inputs 有幾種方式可以保護ADC輸入不受高壓影響。部分ADC(特別是射頻采樣ADC)具有內置電路,可以檢測輸入電壓并在超過設定閾值時進行上報。如數據手冊中所述,該快速檢測輸出存在一些延遲,因此依然會使ADC輸入端短時間內暴漏于高壓之下。

有幾種方式可以保護ADC輸入不受高壓影響。部分ADC(特別是射頻采樣ADC)具有內置電路,可以檢測輸入電壓并在超過設定閾值時進行上報。如數據手冊中所述,該快速檢測輸出存在一些延遲,因此依然會使ADC輸入端短時間內暴漏于高壓之下。

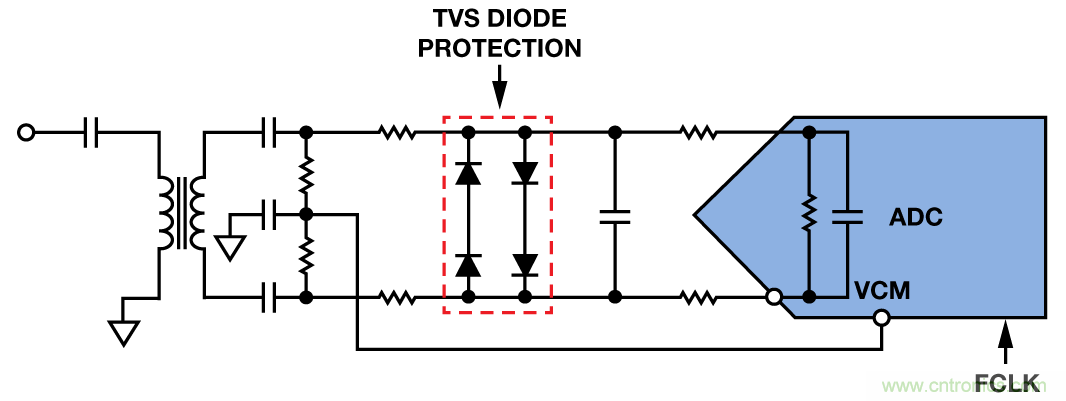

圖6. 帶TVS二極管保護的ADC前端電路

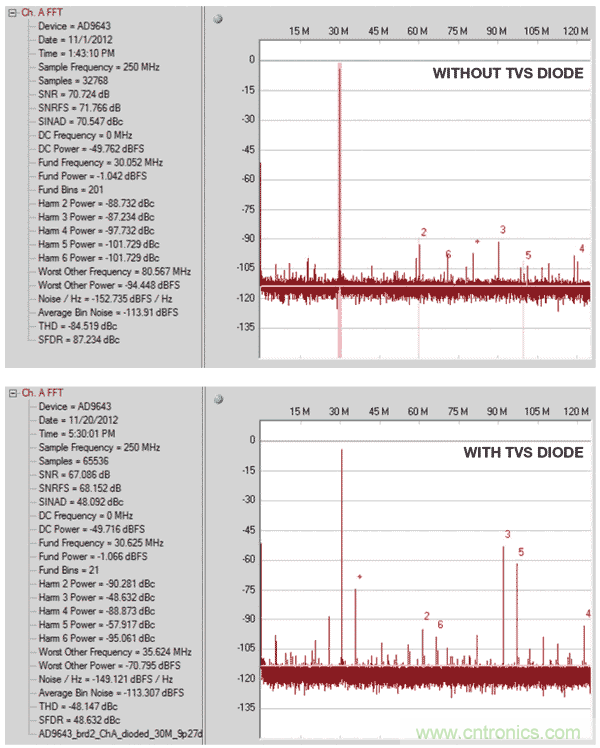

雖然TVS二極管通過箝位過量電壓保護ADC輸入,但它們會極大地惡化諧波性能。圖7顯示了具有30 MHz、–1 dBFS輸入的14位、250 MSPS無緩沖ADC的前端帶與不帶TVS二極管時的FFT比較情況。

圖7. 帶與不帶TVS二極管保護的ADC前端電路FFT比較

TVS二極管會極大地惡化奇次諧波性能,因為它們在不作用為箝位的時候就相當于一反向偏置二極管。該PN二極管具有結電容CJ0,該電容與ADC內部開關動作產生的非線性反沖電流互相作用,產生一個與模擬輸入信號混合的電壓信號。該混合信號在ADC內部被采樣,產生極大的三次諧波。在過壓條件下的時域曲線(圖8)顯示了TVS二極管的箝位削壓的功能。這并不表示TVS二極管不適合用來保護ADC輸入,只是必須仔細考慮二極管規格,以便達到性能要求。選擇二極管類型及其參數時必須作更全面的考慮。

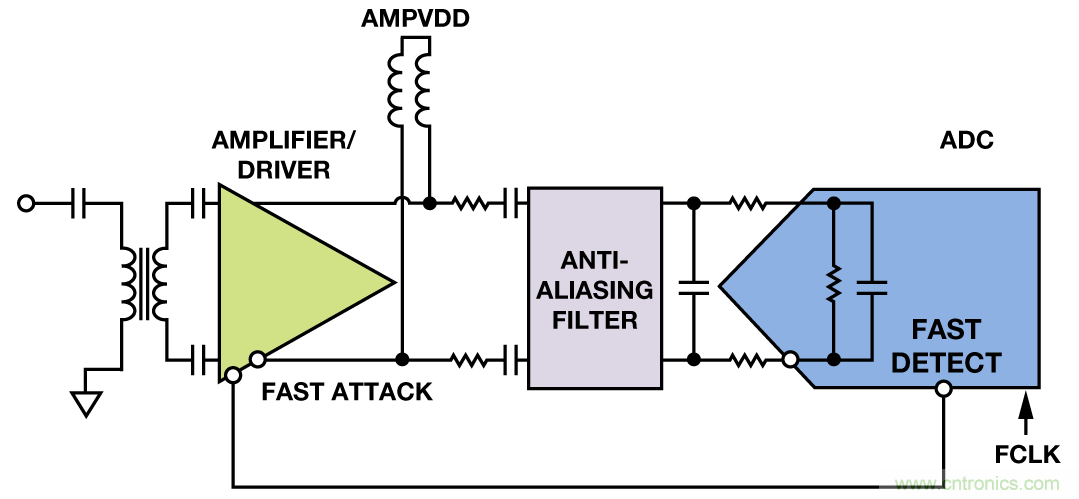

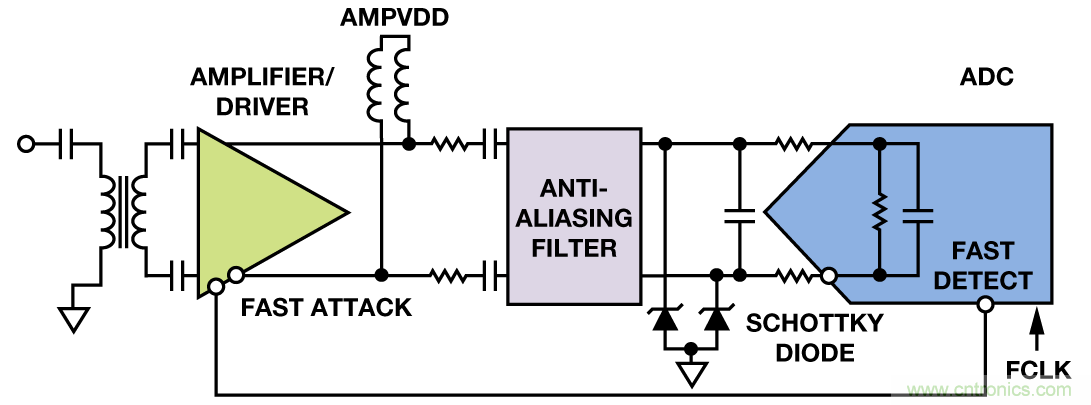

圖8. 前端電路中的TVS二極管保護導致削波信號

當帶寬和采樣速率達到GHz和GSPS級別時,射頻采樣ADC可以簡化無線電接收機設計,因為它們不需要ADC前具有很多的混頻級,但這樣會讓ADC輸入易受過壓應力影響。圖9顯示的是用于射頻采樣ADC的典型前端設計,采用放大器驅動。新一代放大器專為與這些ADC實現接口而設計,具有快速攻擊響應輸入管教,可通過串行外設接口(SPI)配置,將輸出衰減為預定增益。快速攻擊響應引腳可以配置為響應射頻采樣ADC的快速檢測輸出。ADA4961是具有快速攻擊響應功能的新一代放大器實例。AD9680 和 AD9625 是具有快速檢測功能的射頻采樣ADC實例。

圖9. 帶快速攻擊響應功能的放大器驅動帶快速檢測功能的射頻采樣ADC

只要輸入電壓處于合理的范圍之內,圖9中的拓撲便能工作良好。舉例而言,假如該接收機的輸入端收到突發高壓信號,則放大器的輸出將上升至放大器電源軌的電壓水平(本例中為5 V)。這將產生巨大的電壓擺幅,超過ADC輸入端的絕對最大額定電壓。快速檢測功能存在一定延遲(AD9680-1000為28個時鐘周期或28 ns),因此等到快速檢測邏輯輸出告訴放大器置位快速攻擊響應時,ADC早已暴露在高壓下數個時鐘周期。這可能降低ADC的可靠性,因此無法承受這種風險的系統設計必須采用第二保護模式。具有極低器件和寄生電容的快速響應肖特基二極管在這種情況下十分管用。特定二極管的關鍵參數可參見數據手冊。

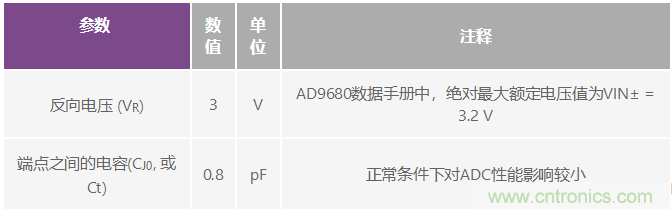

反向擊穿電壓(VBR)——AD9680輸入引腳上的最大輸入電壓——相對于AGND約為3.2 V,因此為該二極管選擇數值為3 V的反向擊穿電壓。

結電容(CJ0)——二極管電容應盡可能低,確保正常工作時二極管不影響ADC的交流性能(SNR/SFDR)。

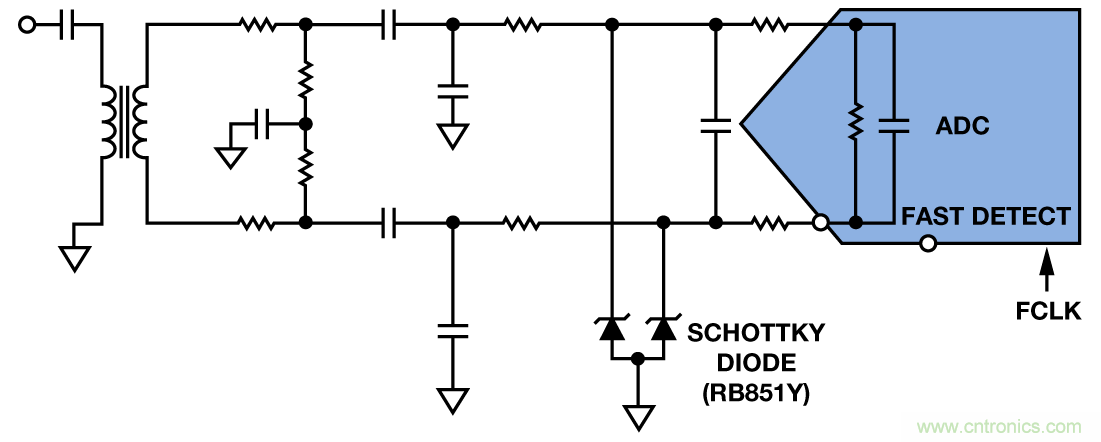

圖10顯示的是無源前端,肖特基二極管位于ADC之前。無源前端比較容易演示肖特基二極管在不影響交流性能情況下對ADC輸入端的保護。

圖10. 顯示射頻采樣ADC和肖特基二極管的無源前端電路

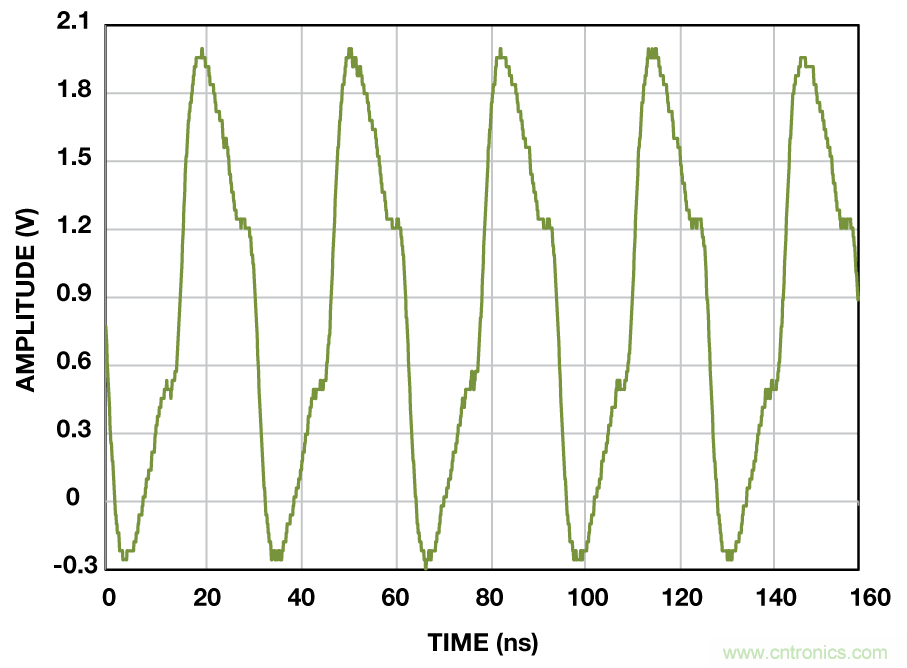

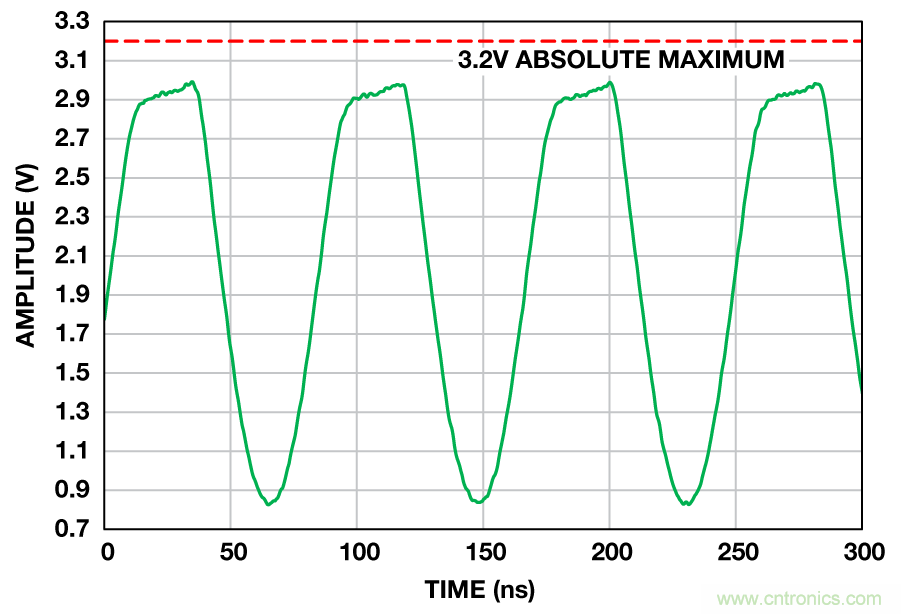

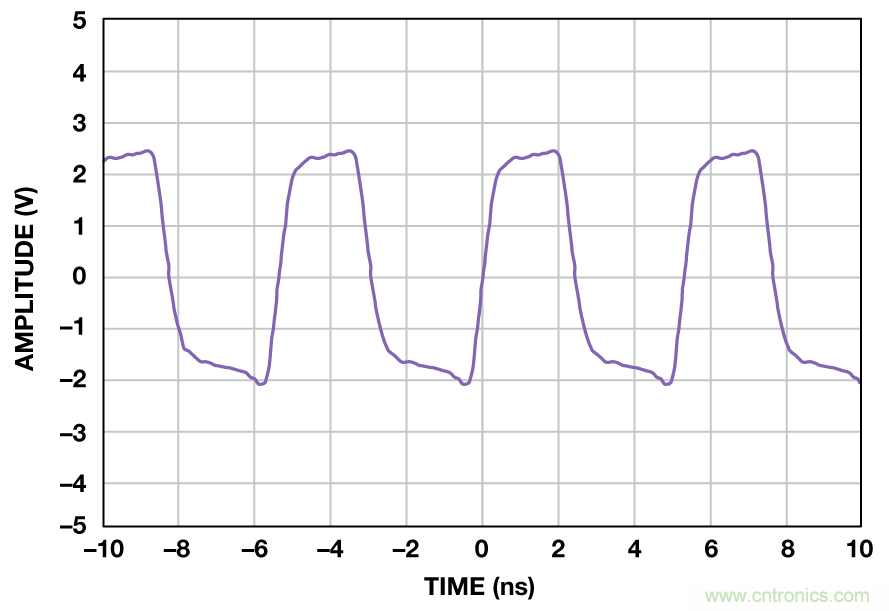

這顆射頻采樣ADC經過測試可輸入高達2 GHz頻率的信號,因此選用RF肖特基二極管(RB851Y)。表2顯示RB851Y的關鍵參數;表明該器件適合該應用。測試結果顯示二極管防止了ADC輸入電壓超過其3.2 V的絕對最大電壓(相對于AGND)。圖11顯示的是一個單端輸入(ADC的VIN+引腳)暴露在高壓之下(185 MHz)的情況。肖特基二極管將電壓箝位至3.0 V左右(相對于AGND),防止ADC輸入達到3.2 V限值。圖12顯示的是在肖特基二極管箝位下的AD9680輸入端的差分信號。

表2. 用于保護射頻采樣ADC輸入的肖特基二極管關鍵參數

圖11. 肖特基二極管箝位的單端ADC輸入

圖12. 肖特基二極管箝位AD9680差分輸入信號

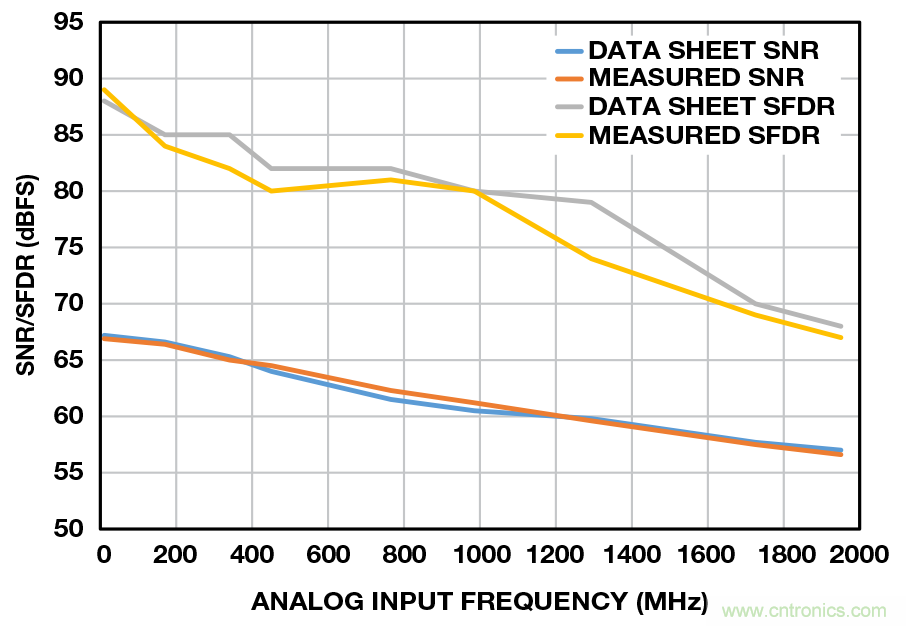

下一步,我們測量正常工作性能。AD9680按照數據手冊中的建議進行控制,但輸入如圖10所示進行修改。模擬輸入頻率變化范圍為10 MHz至2 GHz。CJ0的超低數值應當不會對ADC的SNR和SFDR性能造成影響。

圖13. AD9680帶肖特基二極管保護時SNR/SFDR與模擬輸入頻率的關系

肖特基二極管根本不會影響SNR性能,但某些頻率下SFDR與預期值有所偏差,如圖13所示。這可能是由于差分信號失配或ADC反沖所導致的。評估板是從直流到2 GHz的寬頻段設計,因此當它在整個頻段內的整體工作良好時,某些元器件可能在特定頻率下與肖特基二極管相互作用。

大部分應用不會用到整個2 GHz頻段,因此可以通過修改過壓保護的輸入電路,將前端調諧至所需的目標信號帶寬。謹慎選擇肖特基二極管可以保護ADC輸入,因而系統設計人員可以使用具有最新快速攻擊響應功能和快速檢測功能的放大器驅動前端電路,如圖14所示。

圖14. ADA4961驅動AD9680(顯示射頻采樣ADC和肖特基二極管)

結論

本文討論如何使用肖特基二極管保護射頻采樣ADC輸入,使其免受過壓應力的影響。仔細審查二極管的數據手冊參數很關鍵。為了實現最佳的目標頻段性能,需要對該電路的實施進行規劃。射頻采樣ADC的快速檢測輸出可以與最新放大器的快速攻擊響應功能進行配合,設置自動增益控制環路。

參考電路

Castera, Jim and Rob Reeder. "寬帶ADC前端設計考慮II:用放大器還是用變壓器驅動ADC?" 模擬對話,第41卷第1期,2007年。

Das, Dave Roy. "高速開關電容ADC的低失真緩沖技術." 麻省理工學院,1997年。

Kester, Walt. 數據轉換手冊.ADI公司,2004年。

MT-228: 高速ADC模擬輸入接口考慮因素

Reeder, Rob. "高速無緩沖ADC的反沖." Electronic Design, 2011年。

Reeder, Rob. "測試高速ADC的模擬輸入相位不平衡." UBM Electronics, 2011年。

Shedge, Dnyandeo, Devendra Itole, Milind Gajare, 和 Prakash Wani. "CMOS源極跟隨器和超級源極跟隨器的分析與設計." ACEEE.