【導讀】電源完整性設計的水平直接影響著系統的性能,如整機可靠性、信噪比與誤碼率及EMI/EMC等重要指標。板級電源通道阻抗過高和同步開關噪聲SSN過大會帶來嚴重的電源完整性問題,這些會給器件及系統工作穩定性帶來致命的影響。PI設計就是通過合理的平面電容、分立電容、平面分割應用確保板級電源通道阻抗滿足要求,確保板級電源質量符合器件及產品要求,確保信號質量及器件、產品穩定工作。

電源噪聲問題

隨著超大規模集成電路工藝的發展,芯片工作電壓越來越低,而工作速度越來越快,功耗越來越大,單板的密度也越來越高,因此對電源供應系統在整個工作頻帶內的穩定性提出了更高的要求。電源完整性設計的水平直接影響著系統的性能,如整機可靠性、信噪比與誤碼率及EMI/EMC等重要指標。板級電源通道阻抗過高和同步開關噪聲SSN過大會帶來嚴重的電源完整性問題,這些會給器件及系統工作穩定性帶來致命的影響。PI設計就是通過合理的平面電容、分立電容、平面分割應用確保板級電源通道阻抗滿足要求,確保板級電源質量符合器件及產品要求,確保信號質量及器件、產品穩定工作。

芯片內部有成千上萬個晶體管,這些晶體管組成內部的門電路、組合邏輯、寄存器、計數器、延遲線、狀態機、以及其他邏輯功能。隨著芯片的集成度越來越高,內部晶體管數量越來越大。芯片的外部引腳數量有限,為每一個晶體管提供單獨的供電引腳是不現實的。芯片的外部電源引腳提供給內部晶體管一個公共的供電節點,因此內部晶體管狀態的轉換必然引起電源噪聲在芯片內部的傳遞。

對內部各個晶體管的操作通常由內核時鐘或片內外設時鐘同步,但是由于內部延時的差別,各個晶體管的狀態轉換不可能是嚴格同步的,當某些晶體管已經完成了狀態轉換,另一些晶體管可能仍處于轉換過程中。芯片內部處于高電平的門電路會把電源噪聲傳遞到其他門電路的輸入部分。如果接受電源噪聲的門電路此時處于電平轉換的不定態區域,那么電源噪聲可能會被放大,并在門電路的輸出端產生矩形脈沖干擾,進而引起電路的邏輯錯誤。芯片外部電源引腳處的噪聲通過內部門電路的傳播,還可能會觸發內部寄存器產生狀態轉換。

除了對芯片本身工作狀態產生影響外,電源噪聲還會對其他部分產生影響。比如電源噪聲會影響晶振、PLL、DLL的抖動特性,AD轉換電路的轉換精度等。

電源噪聲來源

絕大多數芯片都會給出一個正常工作的電壓范圍,這個值通常是±5%。例如:對于3.3V電壓,為滿足芯片正常工作,供電電壓在3.13V到3.47V之間,或3.3V±165mV。對于1.2V電壓,為滿足芯片正常工作,供電電壓在1.14V到1.26V之間,或1.2V±60mV。這些限制可以在芯片datasheet中查到。這些限制要考慮兩個部分,第一是穩壓芯片的直流輸出誤差,第二是電源噪聲的峰值幅度。

電源系統的噪聲來源有三個方面:

第一,穩壓電源芯片本身的輸出并不是恒定的,會有一定的波紋。這是由穩壓芯片自身決定的,一旦選好了穩壓電源芯片,對這部分噪聲我們只能接受,無法控制。

第二,穩壓電源無法實時響應負載對于電流需求的快速變化。穩壓電源芯片通過感知其輸出電壓的變化,調整其輸出電流,從而把輸出電壓調整回額定輸出值。多數常用的穩壓源調整電壓的時間在毫秒到微秒量級。因此,對于負載電流變化頻率在直流到幾百KHz之間時,穩壓源可以很好的做出調整,保持輸出電壓的穩定。當負載瞬態電流變化頻率超出這一范圍時,穩壓源的電壓輸出會出現跌落,從而產生電源噪聲。現在,微處理器的內核及外設的時鐘頻率已經超過了600兆赫茲,內部晶體管電平轉換時間下降到800皮秒以下。這要求電源分配系統必須在直流到1GHz范圍內都能快速響應負載電流的變化,但現有穩壓電源芯片不可能滿足這一苛刻要求。我們只能用其他方法補償穩壓源這一不足,這涉及到后面要講的電源去耦。

第三,負載瞬態電流在電源路徑阻抗和地路徑阻抗上產生的壓降。PCB板上任何電氣路徑不可避免的會存在阻抗,不論是完整的電源平面還是電源引線。對于多層板,通常提供一個完整的電源平面和地平面,穩壓電源輸出首先接入電源平面,供電電流流經電源平面,到達負載電源引腳。地路徑和電源路徑類似,只不過電流路徑變成了地平面。完整平面的阻抗很低,但確實存在。如果不使用平面而使用引線,那么路徑上的阻抗會更高。另外,引腳及焊盤本身也會有寄生電感存在,瞬態電流流經此路徑必然產生壓降,因此負載芯片電源引腳處的電壓會隨著瞬態電流的變化而波動,這就是阻抗產生的電源噪聲。在電源路徑表現為負載芯片電源引腳處的電壓軌道塌陷,在地路徑表現為負載芯片地引腳處的電位和參考地電位不同(注意,這和地彈不同,地彈是指芯片內部參考地電位相對于板級參考地電位的跳變)。

如何解決電源噪聲-電容去耦

采用電容去耦是解決電源噪聲問題的主要方法。這種方法對提高瞬態電流的響應速度,降低電源分配系統的阻抗都非常有效。

對于電容去耦,很多資料中都有涉及,但是闡述的角度不同。有些是從局部電荷存儲(即儲能)的角度來說明,有些是從電源分配系統的阻抗的角度來說明,還有些資料的說明更為混亂,一會提儲能,一會提阻抗,因此很多人在看資料的時候感到有些迷惑。其實,這兩種提法,本質上是相同的,只不過看待問題的視角不同而已。為了讓大家有個清楚的認識,介紹一下這兩種解釋。

(1)從儲能角度看電容去耦

在制作電路板時,通常會在負載芯片周圍放置很多電容,這些電容就起到電源去耦作用。

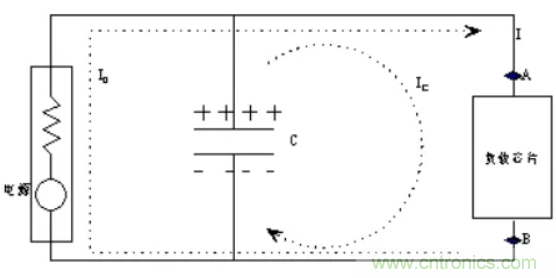

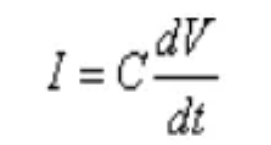

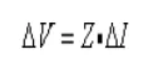

負載電流不變時,其電流由穩壓電源部分提供,即圖中的I0,方向如圖所示。此時電容兩端電壓與負載兩端電壓一致,電流Ic為0,電容兩端存儲相當數量的電荷,其電荷數量和電容量有關。當負載瞬態電流發生變化時,由于負載芯片內部晶體管電平轉換速度極快,必須在極短的時間內為負載芯片提供足夠的電流。但是穩壓電源無法很快響應負載電流的變化,因此,電流I0不會馬上滿足負載瞬態電流要求,因此負載芯片電壓會降低。但是由于電容電壓與負載電壓相同,因此電容兩端存在電壓變化。對于電容來說電壓變化必然產生電流,此時電容對負載放電,電流Ic不再為0,為負載芯片提供電流。根據電容等式:

要電容量C足夠大,只需很小的電壓變化,電容就可以提供足夠大的電流,滿足負載瞬態電流的要求。這樣就保證了負載芯片電壓的變化在容許的范圍內。這里,相當于電容預先存儲了一部分電能,在負載需要的時候釋放出來,即電容是儲能元件。儲能電容的存在使負載消耗的能量得到快速補充,因此保證了負載兩端電壓不至于有太大變化,此時電容擔負的是局部電源的角色。

從儲能的角度來理解電源去耦,非常直觀易懂,但是對電路設計幫助不大。從阻抗的角度理解電容去耦,能讓我們設計電路時有章可循。實際上,在決定電源分配系統的去耦電容量的時候,用的就是阻抗的概念。

(2)從阻抗角度看電容去耦

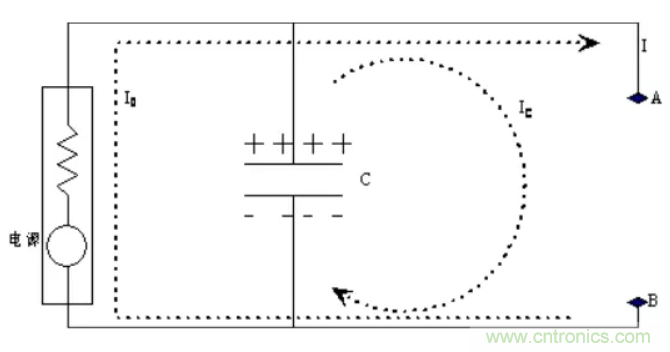

將圖中的負載芯片拿掉,從AB兩點向左看過去,穩壓電源以及電容去耦系統一起,可以看成一個復合的電源系統。這個電源系統的特點是:不論AB兩點間負載瞬態電流如何變化,都能保證AB兩點間的電壓保持穩定,即AB兩點間電壓變化很小。

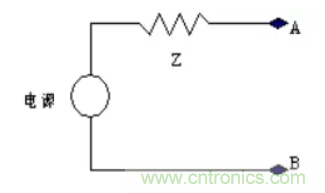

我們可以用一個等效電源模型表示上面這個復合的電源系統,如下圖所示。

對于這個電路可寫出如下等式;

總結

我們的最終設計目標是,不論AB兩點間負載瞬態電流如何變化,都要保持AB兩點間電壓變化范圍很小,根據公式,這個要求等效于電源系統的阻抗Z要足夠低。在圖中,我們是通過去耦電容來達到這一要求的,因此從等效的角度出發,可以說去耦電容降低了電源系統的阻抗。另一方面,從電路原理的角度來說,可得到同樣結論。電容對于交流信號呈現低阻抗特性,因此加入電容,實際上也確實降低了電源系統的交流阻抗。

從阻抗的角度理解電容去耦,可以給我們設計電源分配系統帶來極大的方便。實際上,電源分配系統設計的最根本的原則就是使阻抗最小。最有效的設計方法就是在這個原則指導下產生的。

推薦閱讀: