【導(dǎo)讀】開關(guān)電源的電磁干擾測(cè)試可分為傳導(dǎo)測(cè)試與輻射測(cè)試,一般開關(guān)電源的傳導(dǎo)測(cè)試頻段是指150K~30MHz之間,而輻射干擾的頻段是指30M~300MHz,300MHz之后的頻段一般皆不是電源所產(chǎn)生,因此大都可以給予忽略。下面內(nèi)容章節(jié)包括開關(guān)電源的傳導(dǎo)測(cè)試法規(guī),測(cè)試與量測(cè)方式,基本概念,抑制傳導(dǎo)干擾的濾波器設(shè)計(jì),布線與變壓器設(shè)計(jì)等章節(jié)。

1 前言

電源產(chǎn)品在做驗(yàn)證時(shí),經(jīng)常會(huì)遭遇到電磁干擾(EMI)的問題,有時(shí)處理起來需花費(fèi)非常多的時(shí)間,許多工程師在對(duì)策電磁干擾時(shí)也是經(jīng)驗(yàn)重于理論,知道哪個(gè)頻段要對(duì)策那些組件,但對(duì)于理論上的分析卻很欠缺。筆者從事開關(guān)電源設(shè)計(jì)多年,希望能藉由之前對(duì)策的經(jīng)驗(yàn)與相關(guān)理論基礎(chǔ)做個(gè)整理,讓目前正從事或未來想從事開關(guān)電源設(shè)計(jì)的人員對(duì)電磁干擾防制技術(shù)能有初步的認(rèn)識(shí)。

開關(guān)電源的電磁干擾測(cè)試可分為傳導(dǎo)測(cè)試與輻射測(cè)試,一般開關(guān)電源的傳導(dǎo)測(cè)試頻段是指150K~30MHz之間,而輻射干擾的頻段是指30M~300MHz,300MHz之后的頻段一般皆不是電源所產(chǎn)生,因此大都可以給予忽略。

下面內(nèi)容章節(jié)包括開關(guān)電源的傳導(dǎo)測(cè)試法規(guī),測(cè)試與量測(cè)方式,基本概念,抑制傳導(dǎo)干擾的濾波器設(shè)計(jì),布線與變壓器設(shè)計(jì)等章節(jié)。

2 傳導(dǎo)測(cè)試的法規(guī)

傳導(dǎo)的法規(guī)因產(chǎn)品別的不同,其所適用之條文亦不同,一般是使用歐洲的EN-55022或是美國(guó)的FCC part15來定義其限制線,又可以區(qū)分為CLASS A與CLASS B兩種標(biāo)準(zhǔn),CLASS A為產(chǎn)品在商業(yè)與工業(yè)區(qū)域使用,CLASS B為產(chǎn)品在住宅及家庭區(qū)域使用,筆者所設(shè)計(jì)的產(chǎn)品為3C的家用電源,傳導(dǎo)測(cè)試頻段為150K~30MHz,在產(chǎn)品測(cè)試前請(qǐng)先確認(rèn)申請(qǐng)的安規(guī)為何,不同的安規(guī)與等級(jí)會(huì)有不同的標(biāo)準(zhǔn)線。

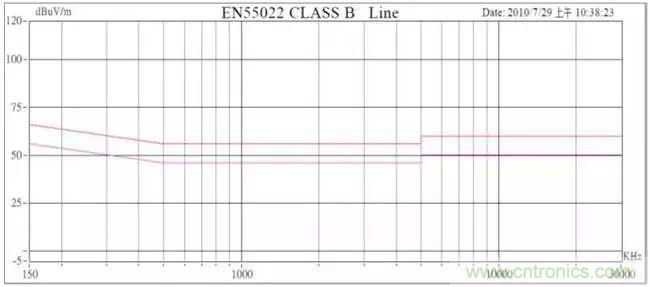

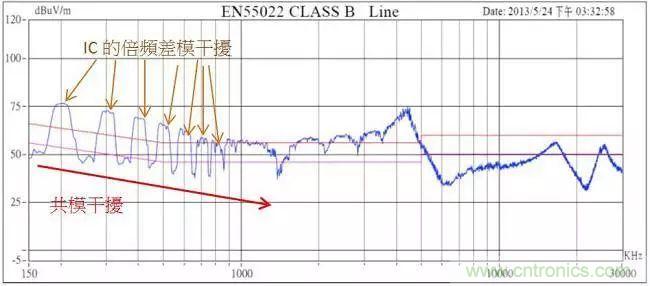

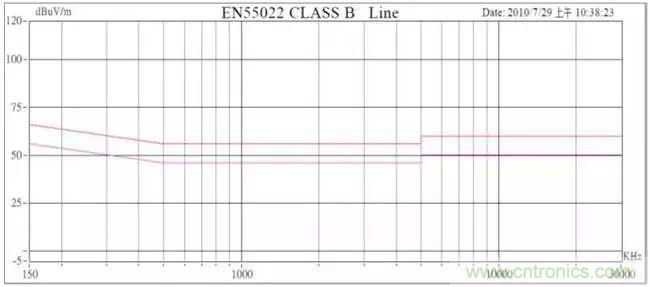

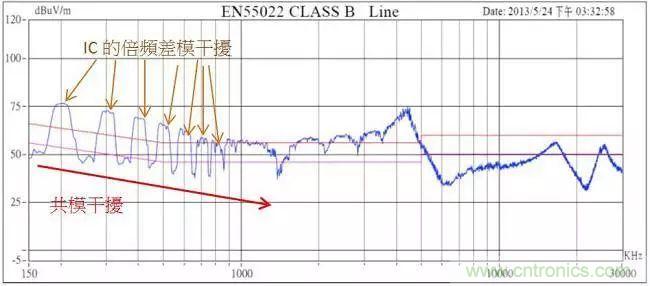

圖1舉例為EN-55022 CLASS B的限制線圖,紅色線為準(zhǔn)峰值(QP, Quasi-peak)的限制線,粉紅色為平均值(AV, Average)的限制線,傳導(dǎo)測(cè)試最終的目地,就是測(cè)試的機(jī)臺(tái)可以完全的低于其限制線,不論是QP值或AV值;一般在申請(qǐng)安規(guī)時(shí),雖然只有在限制線下方即可申請(qǐng),但多數(shù)都會(huì)做到低于2dB的誤差以預(yù)防測(cè)試場(chǎng)地不同所導(dǎo)致的差異,而客戶端有時(shí)會(huì)要求必需低于4~6dB來預(yù)防產(chǎn)品大量生產(chǎn)后所產(chǎn)生的誤差。

圖1

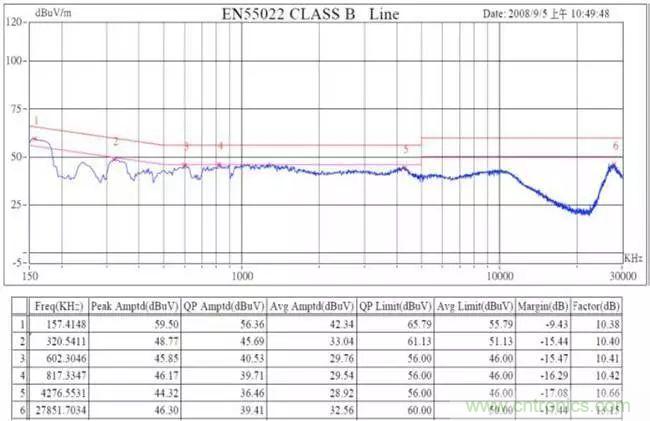

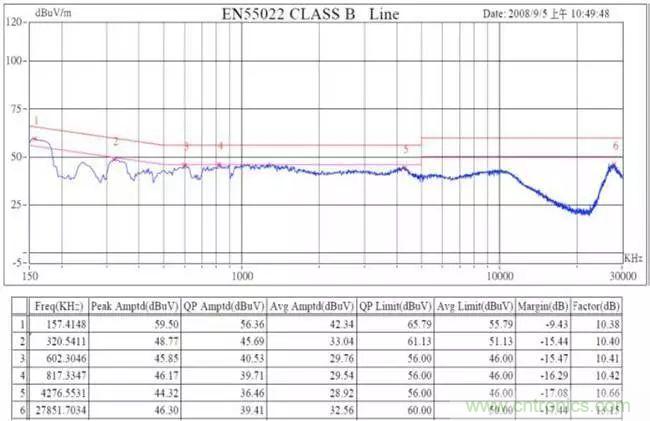

圖2

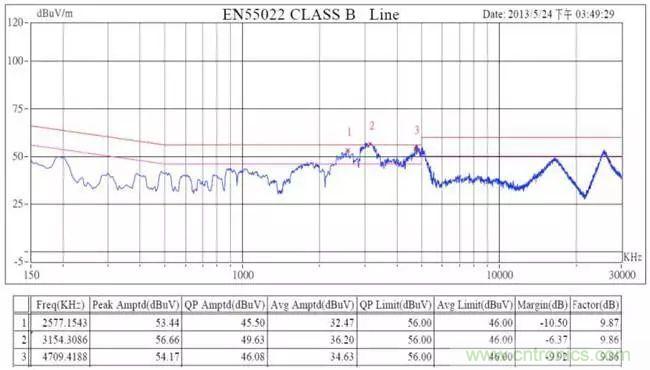

圖2為一量測(cè)后的例子,一般量測(cè)時(shí)都會(huì)先用峰值量測(cè),因峰值量測(cè)是最簡(jiǎn)單且快速的方法,量測(cè)儀器以9KHz為一單位,在150K~30MHz之間用保持最大值(maximum hold)的方式來得到傳導(dǎo)的峰值讀值,用此來確認(rèn)電源的最大峰值然后再依此去抓最高峰值的實(shí)際QP,AV值來減少掃描時(shí)間,圖2的藍(lán)色曲線為準(zhǔn)峰值的峰值量測(cè)結(jié)果,一般在峰值量測(cè)完后會(huì)再對(duì)較高的6個(gè)頻率點(diǎn)做準(zhǔn)峰值(QP)與平均值(AV)的量測(cè),就如同圖2所標(biāo)示。

峰值與準(zhǔn)峰值的差別在于:峰值量測(cè)是不論時(shí)常出現(xiàn)或是偶爾出現(xiàn)的信號(hào)皆被以最大值的方式置在接收器的讀值中,而準(zhǔn)峰值量測(cè)是指在一時(shí)間內(nèi)取數(shù)次此頻段的脈沖信號(hào),若某頻率的信號(hào)在一段時(shí)間內(nèi)重復(fù)出現(xiàn)率較高,才會(huì)得到較高之量測(cè)值;平均值則是對(duì)此頻段的振幅取平均值,典型的頻譜分析儀可將帶寬設(shè)定在30Hz左右來得到最真實(shí)的平均信號(hào)。

QP與AV相較于峰值,其偵測(cè)值必然較低,若一開始的峰值量測(cè)已有足夠的余度則不用再做單點(diǎn)的QP和AV量測(cè)。

現(xiàn)在的IC為了EMI傳導(dǎo)的防制,在操作頻率上都會(huì)做抖頻的功能,像是IC主頻為65KHz,但在操作時(shí)會(huì)以65KHz正負(fù)6K做變化,藉此來將差模倍頻的信號(hào)打散,不會(huì)集中在單一根頻率上,如果沒有抖頻功能,差模干擾在主頻的倍頻時(shí)會(huì)呈現(xiàn)單根很扎實(shí)的QP與AV,如同圖2的157KHz,儀器看到的峰值滿高的,但讀起來還仍有9dB以上的余度。

3 傳導(dǎo)的測(cè)試與量測(cè)方式

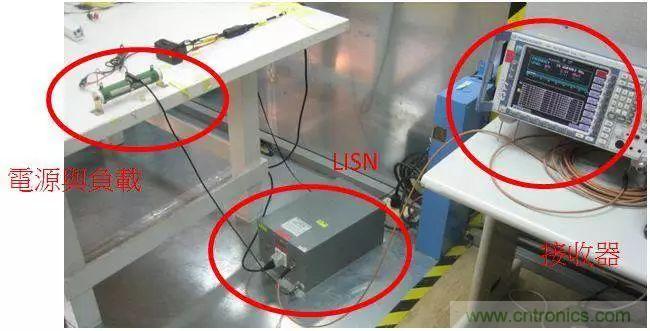

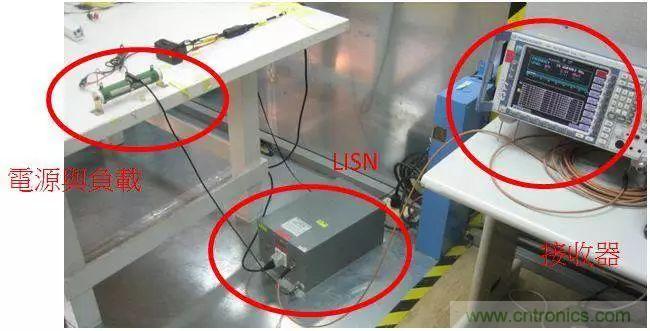

圖3為測(cè)試傳導(dǎo)的參考圖示,此為通嘉內(nèi)部的傳導(dǎo)設(shè)備圖示,待測(cè)物接仿真負(fù)載后放于桌面上,經(jīng)由一輸入線材(AC cable)連接LISN(線性阻抗穩(wěn)定網(wǎng)絡(luò))與待測(cè)物,再將LISN的信號(hào)接至接收器,輸入線材不得與地面接觸,而待測(cè)物的負(fù)載需與待測(cè)物距離10公分,若周邊需接電源時(shí),其電源需接獨(dú)立電源,不得與待測(cè)物使用相同電源,若電源為2PIN輸入,則輸出負(fù)載需接地以仿真系統(tǒng)下地。

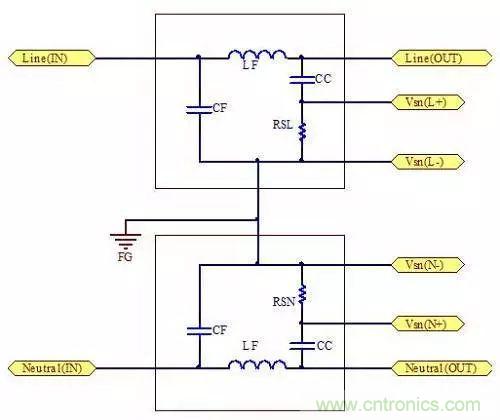

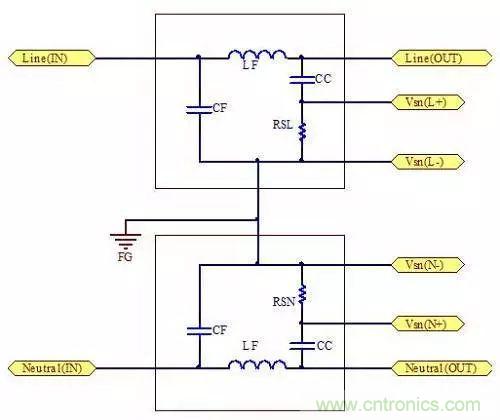

LISN(線性阻抗穩(wěn)定網(wǎng)絡(luò))內(nèi)部線路如圖4所示,輸入電源來源由左邊進(jìn)入LISN后,經(jīng)由LF與CF來濾除電源的低頻噪聲,并由耦合電容CC與偵測(cè)電阻RSL/RSN來取得高頻信號(hào)Vsn,再將此信號(hào)經(jīng)接受器或頻譜分析儀來得到其振幅的大小(dBuV)。

圖3

圖4

請(qǐng)記得輸入線材不得與地面接觸,筆者曾有過輸入線材與地面接觸與否,讀值差了10dB左右的經(jīng)驗(yàn);另外,周邊儀器的電源需使用干凈且與主電源隔離的電源,否則很容易因共地而產(chǎn)生共模干擾,許多測(cè)試場(chǎng)地會(huì)直接拿一個(gè)延長(zhǎng)線去使用外接電源給予周邊,但此種方式仍有可能因共地而被干擾,若能使其接至另一個(gè)LISN是個(gè)較好的方式,因LISN內(nèi)有LF與CF可作信號(hào)隔離。

4 對(duì)策EMI傳導(dǎo)的基本概念

4.1 差模(Differential mode)信號(hào)與共模(Common mode)信號(hào)

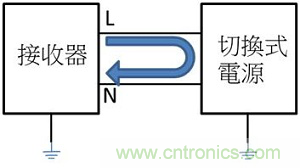

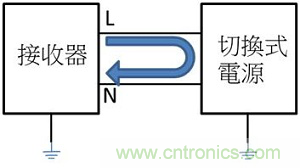

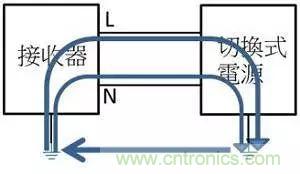

傳導(dǎo)量測(cè)接法如圖5、圖6所示,是由接收器量測(cè)L/N/GND之間的頻率與振幅大小而成,而信號(hào)存在于L與N之間的叫差模信號(hào),如圖5所示;而信號(hào)存在于L與FG或N與FG之間的叫共模信號(hào),如圖6所示,也可以說與FG形成回路的就叫共模信號(hào)。

一般電源的輸入來源皆是取自L與N,因此在電源的電磁干擾設(shè)計(jì)中,差模成份的抑制極為重要,尤其是前頻段150K~1MHz大多是由開關(guān)電源的主頻與倍頻出來的差模干擾。

圖5

圖6

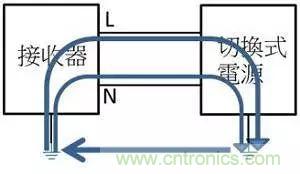

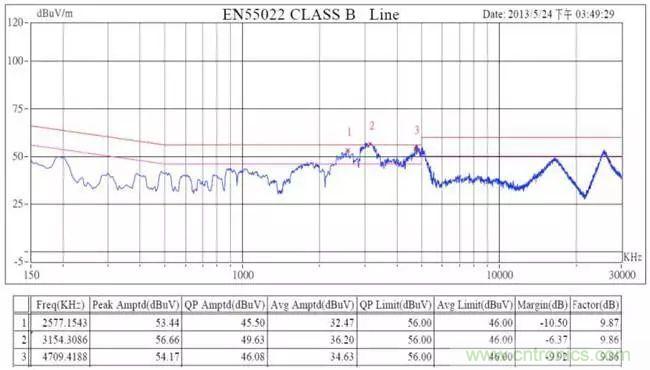

圖7為一未對(duì)策前的傳導(dǎo)測(cè)試結(jié)果,前端為IC的操作頻率所引起的倍頻差模干擾加上本體的共模干擾所形成,由圖形可看出每根峰值之間的頻率為100KHz,可判斷此IC的操作頻率為100KHz,而測(cè)量的讀值是呈現(xiàn)由IC 100KHz的倍頻做線性衰減,因此每100KHz就有一根因IC操作頻率所造成的差模干擾信號(hào),也可以說在前頻段時(shí),共模信號(hào)呈線性平面下降,而差模信號(hào)則迭加在共模的上方。

圖7

圖8為相同的機(jī)臺(tái)在對(duì)策后測(cè)試結(jié)果,在對(duì)策后最差都還有6dB以上的余度,已可符合多數(shù)的客戶要求。

一般在測(cè)試時(shí),必需測(cè)試L與N兩項(xiàng),一般L與N的讀值不會(huì)差異太大,若差異很大一般都是某項(xiàng)的共模能量較強(qiáng)所致。

測(cè)試的輸入電壓則是看申請(qǐng)的安規(guī)來決定,一般是用110V與230V來做高低壓量測(cè);另外,產(chǎn)品在確認(rèn)傳導(dǎo)測(cè)試時(shí)皆需要做長(zhǎng)時(shí)間的燒機(jī),有時(shí)會(huì)因燒機(jī)后磁性組件過熱導(dǎo)致感量異常而讓EMI變差。

圖8

4.2 電磁干擾,電場(chǎng)干擾與磁場(chǎng)干擾

電磁干擾(EMI, Electrical Magnetic Interference)可分為電場(chǎng)干擾與磁場(chǎng)干擾兩種,電場(chǎng)與磁場(chǎng)是兩種不同的性質(zhì),但兩者之間的能量是會(huì)互相影響的,隨時(shí)間變化的電場(chǎng)會(huì)產(chǎn)生磁場(chǎng),而隨時(shí)間變化的磁場(chǎng)也會(huì)產(chǎn)生電場(chǎng),這些不斷同相振蕩的電場(chǎng)和磁場(chǎng)共同的形成了電磁干擾(電磁波)。

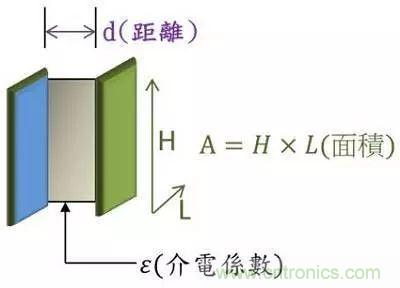

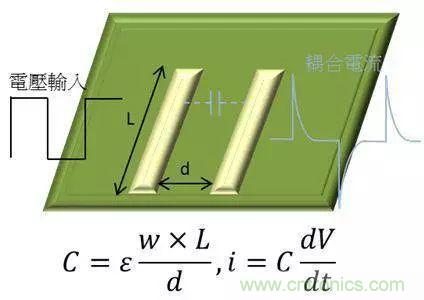

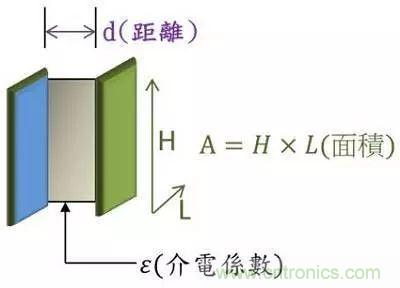

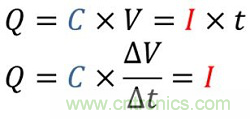

一般對(duì)于電場(chǎng),我們可以用下面的電荷公式與電容公式來作解釋,簡(jiǎn)單來說,任何的導(dǎo)體在電場(chǎng)下都可等效成一個(gè)帶電的電容,其容值隨著與周邊另一個(gè)導(dǎo)體之間的距離/表面積/介質(zhì)不同而有差異;如圖9為兩導(dǎo)體之間的電容圖示,綠色導(dǎo)體與藍(lán)色導(dǎo)體所等效的電容如圖10所示,根據(jù)電容公式,容值會(huì)因兩導(dǎo)體之間的距離愈遠(yuǎn)而變小,也會(huì)因兩導(dǎo)體之間的截面積愈大而增大,而兩導(dǎo)體之間的介質(zhì)(介電系數(shù))也會(huì)影響容值的大小。

圖9

圖10

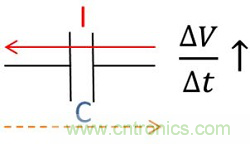

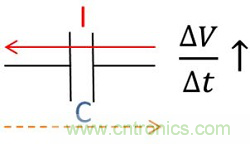

當(dāng)電容二端的電位在時(shí)間之內(nèi)存在一電壓差時(shí),則會(huì)根據(jù)電荷公式(電壓/時(shí)間的變化,如圖12)而產(chǎn)生一電流,如圖11紅色箭頭所示,而任何產(chǎn)生的電流必需經(jīng)由另一路徑回到自己出發(fā)時(shí)的位置而形成一電流回路,如棕色虛線箭頭所示,此因電壓變動(dòng)造成的電流回路就會(huì)引起電場(chǎng)干擾。

圖11

圖12

因此,改善電場(chǎng)干擾的方式,就是減少其回路電流的方法,根據(jù)上面兩個(gè)公式,我們可以藉由將耦合電容減小,像是減少兩個(gè)導(dǎo)體之間接觸的面積/增加其距離/變更中間的介質(zhì)等方式來減少電容效應(yīng),或是減小電壓差或時(shí)間變化率來減少電場(chǎng)感應(yīng)。

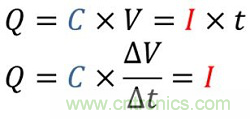

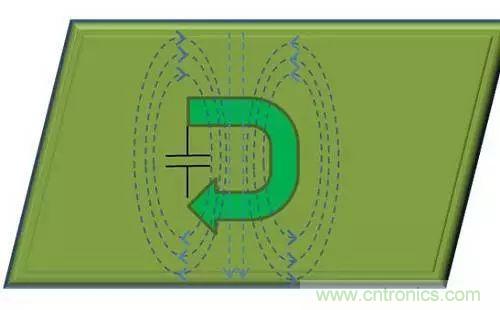

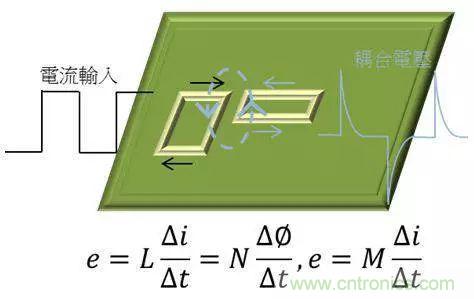

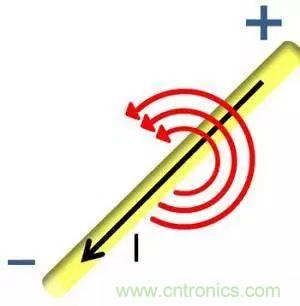

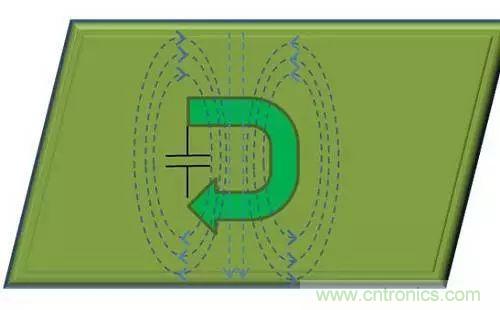

而對(duì)于磁場(chǎng),我們可用安培右手/法拉第定律來解釋,當(dāng)導(dǎo)體有電流流過時(shí),在其周圍就會(huì)依安培右手定律產(chǎn)生磁力線,如圖13所示,因電流不可能單獨(dú)存在,電流一定存在于回路之中,凡是電流流過的路徑都會(huì)產(chǎn)生磁力線,而在一般的PCB板設(shè)計(jì)中(如圖14所示),當(dāng)電容形成一個(gè)電流回路時(shí)就會(huì)產(chǎn)生如虛線的磁力線,而磁力線經(jīng)過的導(dǎo)體會(huì)因此產(chǎn)生感應(yīng)電勢(shì),此即為磁場(chǎng)干擾。

圖13

圖14

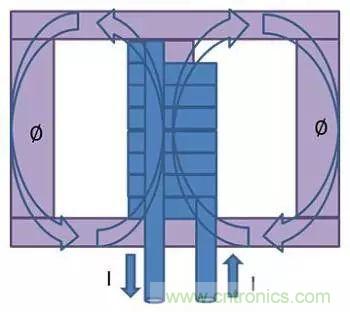

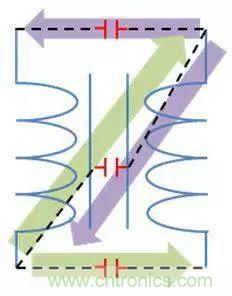

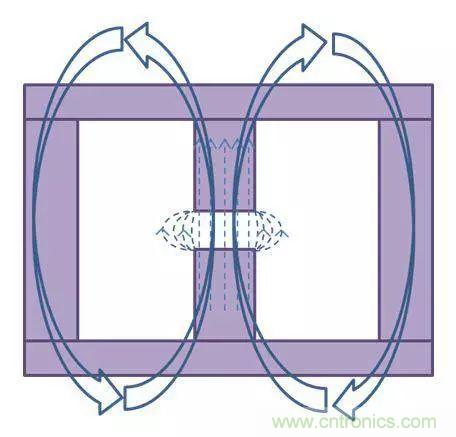

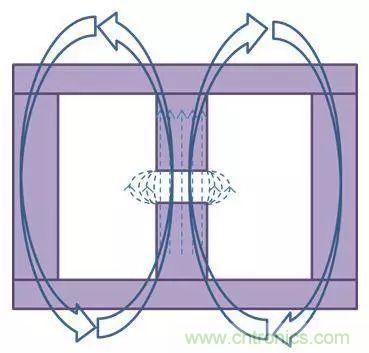

尤其是電流流經(jīng)的導(dǎo)體在沒有閉合回路的鐵心時(shí),因磁力線無法經(jīng)由高導(dǎo)磁材料做回路,磁力線會(huì)經(jīng)由外部空氣做回路而讓周圍產(chǎn)生磁場(chǎng)(漏磁通),圖15所示為一般變壓器的磁力線,大多數(shù)的磁力線皆會(huì)經(jīng)由高導(dǎo)磁材料(鐵心),但在中間有氣隙的地方就會(huì)有許多漏磁通產(chǎn)生(如圖16虛線所示),而也有少部份漏磁通會(huì)經(jīng)過與變壓器垂直的地方,因此若有組件在變壓器的正上方或下方,是很容易被此漏磁通干擾的。

圖15

圖16

因此,改善磁場(chǎng)干擾的方式,包括兩部份,一是減少磁力線的能量,包括改變電流振幅/時(shí)間變化率等,另一是減少磁力線的影響,包括縮小電流回路,拉開兩者之間的距離,導(dǎo)體面積等方法。

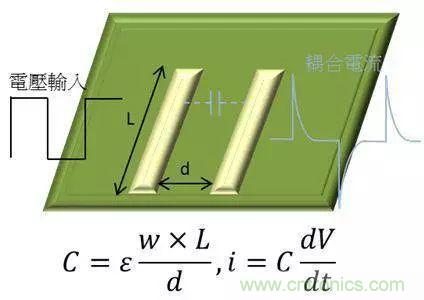

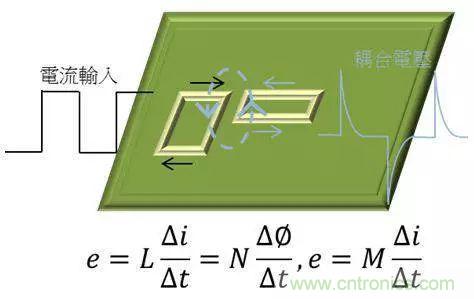

電場(chǎng)耦合效應(yīng)如圖17所示,在PCB板上有兩導(dǎo)體時(shí)會(huì)有一等效電容效應(yīng),而當(dāng)左端的布線有一時(shí)變電壓產(chǎn)生時(shí),其右邊的導(dǎo)體會(huì)因電場(chǎng)耦合效應(yīng)而產(chǎn)生一耦合電流,此耦合電流即是因電場(chǎng)效應(yīng)所產(chǎn)生的電場(chǎng)干擾。

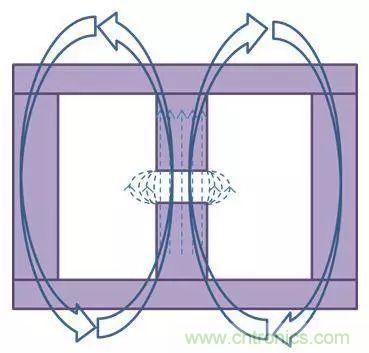

磁場(chǎng)耦合效應(yīng)如圖18所示,在PCB板上有兩導(dǎo)體回路時(shí),當(dāng)左邊的回路有一時(shí)變電流產(chǎn)生,其右邊的回路也會(huì)因磁場(chǎng)耦合效應(yīng)而產(chǎn)生一耦合電壓(感應(yīng)電勢(shì)),此電壓即是因磁場(chǎng)效應(yīng)所產(chǎn)生的磁場(chǎng)干擾。

圖17

圖18

產(chǎn)生電場(chǎng)干擾的原因,在于帶電體的電荷重新分布,因電荷改變后會(huì)讓電容兩端的電壓改變而不斷的充放電。產(chǎn)生磁場(chǎng)干擾的原因,在于流過導(dǎo)體的電流在不斷改變,即電流產(chǎn)生的磁力線會(huì)使周圍導(dǎo)體感應(yīng)出電動(dòng)勢(shì),告成磁場(chǎng)干擾。

電場(chǎng)與磁場(chǎng)的干擾起源于快速的能量(電壓/電流)變化;而快速的能量變化可分兩部份,一是能量本體的頻率(變化率),一是能量本體的振幅(大小),而對(duì)策電磁干擾的方式不外兩種,一是對(duì)策能量本體,像是抑制此能量的振幅或是改變其變化率,像是緩沖器,導(dǎo)通(截止)速度,更換組件的速度,變壓器設(shè)計(jì)等,另一是截?cái)喔蓴_的耦合路徑,將干擾源封閉在電源本體里面,像是用LC濾波器,銅箔,外殼等,不論使用何種方式,目的都是為了達(dá)到電磁干擾可以通過法規(guī)的需求。

4.3 寄生組件的影響

在實(shí)際的電源產(chǎn)品中,到處都充滿了寄生組件,包括組件本體的寄生組件與布線組成的寄生成份。當(dāng)頻率到MHz時(shí),nH的電感與pF的電容會(huì)對(duì)EMI產(chǎn)生非常大的影響。

以一個(gè)環(huán)形電感來舉例,多數(shù)的工程師只在意它的Al值,即繞了幾圈后可以得到多少的感量,卻沒有去考慮到他的等效電容(ESC)與等效電阻(ESR),而在電磁干擾的領(lǐng)域,此等效電容與等效電阻卻非常重要;理想的磁性組件,其阻抗應(yīng)與頻率成正比(Xl=2*pi*f*L),即頻率愈高時(shí)其阻抗愈高,但在實(shí)際應(yīng)用里,組件的等效電容卻會(huì)抑制其阻抗特性。

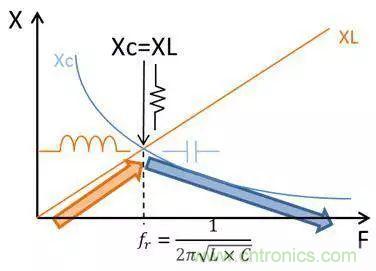

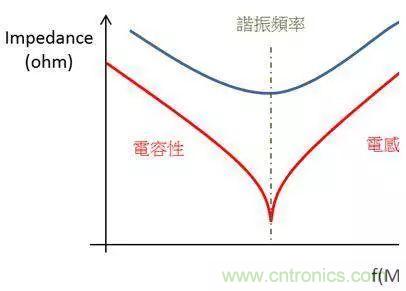

如圖19為一電感的阻抗與頻率曲線,在頻率低于共振點(diǎn)時(shí),其阻抗會(huì)因頻率上升而增加,但在過了共振點(diǎn)(Fr)后,阻抗卻會(huì)因頻率上升而變小,而無法達(dá)到預(yù)期的抑制效果。

圖19

筆者在對(duì)策電磁干擾時(shí)將頻段分為二部份, 10M以下的頻段與10M以上的頻段,在10M以下的頻段, 其對(duì)策與變壓器/濾波器/布線/結(jié)構(gòu)等較相關(guān), 而在10M以上的頻段, 其對(duì)策與變壓器/布線/濾波器/緩沖器(Snubber&Bead)/開關(guān)組件與速度/屏敝等較相關(guān), 因布線/濾波器/變壓器在高低頻皆會(huì)影響,因此筆者在此先針對(duì)布線/濾波器/變壓器等(10M以下)先做介紹。

5 布線(Layout)設(shè)計(jì)概念

由之前的介紹可知,電場(chǎng)干擾與磁場(chǎng)干擾是電磁干擾里最大的干擾源,不但布線的走線會(huì)大大的影響電場(chǎng)與磁場(chǎng)的耦合路徑,也會(huì)因布線的寄生組件而影響電源的特性,因此良好的布線方式是從事電源設(shè)計(jì)不可缺少的能力之一,不但多數(shù)的電性問題皆因不良的布線導(dǎo)致,電磁干擾的好壞也與布線習(xí)習(xí)相關(guān),不論是傳導(dǎo)或輻射。

多數(shù)的布線工程師并不知道怎樣的走線方式較好,而只認(rèn)為每個(gè)節(jié)點(diǎn)都接到即可,愈資深的工程師則愈會(huì)對(duì)布線有所要求,以作者的經(jīng)驗(yàn),60%以上的電性不良皆是因布線所致,而在此將布線的基本概念概述如下:

5.1 安規(guī)距離與制程要求

此為最基本要求,任何產(chǎn)品皆需要達(dá)到安規(guī)規(guī)范,而不同的產(chǎn)線也會(huì)有不同的制程要求,像是組件本體大小,各組件之間的距離,接點(diǎn)大小,白漆…等,一般此規(guī)范會(huì)由各家布線工程師管控,因此在這里不做多述。

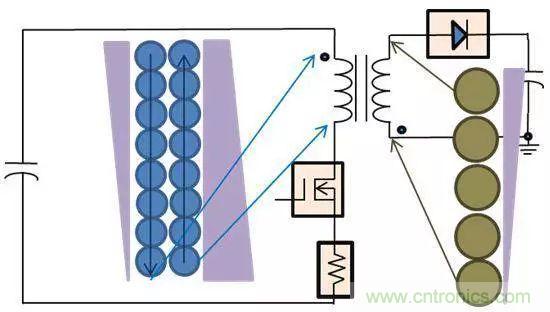

5.2 電源路徑與信號(hào)路徑需分開

在開關(guān)電源設(shè)計(jì)里,信號(hào)可分為大電流與小電流的,以 反激式(flyback)架構(gòu)為例,大電流是由輸入電源進(jìn)來至濾波器,橋式,大電容,變壓器,初級(jí)側(cè)開關(guān),次級(jí)側(cè)二極管,輸出電容到輸出線材等走大電流的路徑稱為電源路徑(power trace);而走小電流的路徑就稱為信號(hào)路徑(signal trace),像是IC周邊的組件或回授電路。

電壓愈大會(huì)有較大電場(chǎng)的產(chǎn)生,而電流愈大則會(huì)有愈大磁場(chǎng)的產(chǎn)生,而周邊組件,特別是良導(dǎo)體愈靠近此電場(chǎng)或磁場(chǎng)就會(huì)耦合愈大的能量,因此在做布線安排時(shí),盡量讓電源路徑與信號(hào)路徑分開來走,以免信號(hào)路徑被干擾產(chǎn)生誤動(dòng)作,也避免干擾源藉由其他導(dǎo)體放大其干擾信號(hào),在此將電源路徑與信號(hào)路徑分別說明如下:

5.2.1 電源路徑的基本概念

把布線的路徑想象成一條水流(即電流),水流自然會(huì)往河流愈寬的地方流(走線愈粗的地方),而且也自然會(huì)往低處流(往目標(biāo),即輸出端流),在電源路徑上的組件皆應(yīng)該照順序流過,否則會(huì)大大地衰減其作用。

電容是儲(chǔ)存電荷的組件,愈大的電容可儲(chǔ)存愈多的電荷,因此在看電源路徑時(shí),可視電流由電容正端出發(fā),經(jīng)由開關(guān)組件的回路后再回到電容的負(fù)端形成開關(guān)回路。

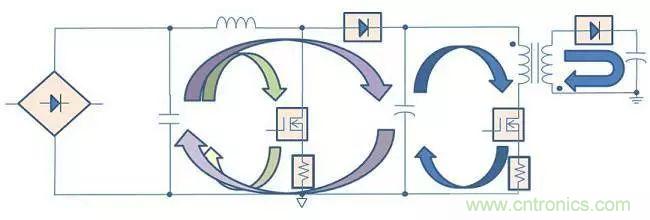

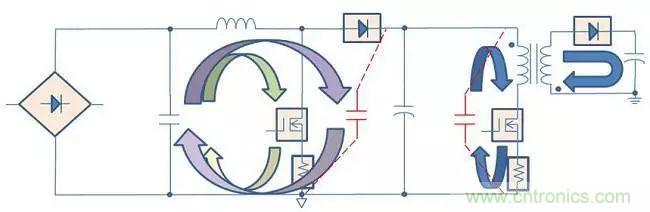

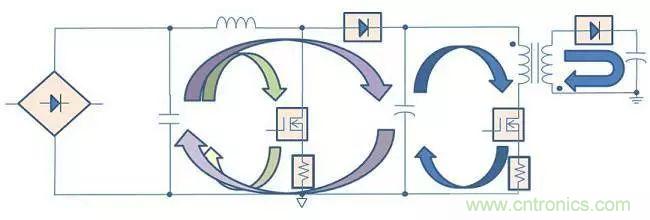

圖20為一升壓加反激(PFC+Flyback)架構(gòu)的例子,PFC前端會(huì)有一顆小電容,PFC會(huì)由此電容形成一導(dǎo)通回路(綠色箭頭)經(jīng)電感,MOSFET,Rsense回小電容,與截止回路(紫色箭頭)經(jīng)電感,二極管,大電容回小電容;即電流由電容的正端出發(fā),經(jīng)一回路之后再回到電容的負(fù)端;同理,F(xiàn)lyback由大電容的正端開始,經(jīng)變壓器,MOSFET,Rsense后再回到大電容負(fù)端;輸出則由變壓器的正端,經(jīng)輸出二極管,輸出電容后回到變壓器的負(fù)端。

圖20

因電源路徑有很大的電流與電壓變動(dòng),因此在布線時(shí)要注意,流過大電流的回路會(huì)產(chǎn)生磁場(chǎng)輻射,因此大電流的走線要盡量短與粗,尤其是次級(jí)側(cè)。

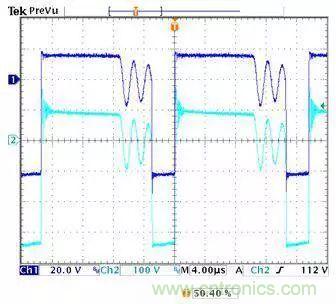

高電壓開關(guān)的走線則要盡量減少其面積以減少電場(chǎng)效應(yīng),并盡量減少其相臨的導(dǎo)體面積與之間的距離以減少等效電容,圖21與22為量測(cè)反激式變壓器兩端的電壓波形,由波形可知在MOSFET的Drain端與Diode的正端有很大的電壓變化量,因此在布線時(shí)此兩點(diǎn)的布線面積要盡可能的小,也盡量遠(yuǎn)離其他的導(dǎo)體以避免電場(chǎng)效應(yīng)。

圖21

圖22

有時(shí)因?yàn)椴季€的考慮,無法將回路變的很短,這時(shí)我們可以靠高頻電容來幫忙,像是在大電解電容同電位上并聯(lián)一個(gè)陶質(zhì)(高頻)電容,因多數(shù)的電解電容是低頻組件,而并聯(lián)的高頻電容可以提供開關(guān)時(shí)的高頻電流,此電容可放在如圖23所示的位置,在PFC端可在二極管后端并一顆小電容且靠近PFC MOSFET的地,縮短PFC截止時(shí)的回路,而Flyback端則可以在靠近變壓器正與Rsense負(fù)端并一顆電容來形成較短的回路;愈短的回路可以減少電場(chǎng)導(dǎo)體與磁場(chǎng)回路的面積來得到更好的EMI效果。

圖23

5.2.2 信號(hào)路徑的基本概念

凡不是電源路徑(Power trace),皆可稱為信號(hào)路徑(Signal trace),因IC是擷取電源路徑里的電壓/電流信號(hào)來維持系統(tǒng)的穩(wěn)定,因此在信號(hào)路徑里最重要的就是從擷取信號(hào)源到各IC 腳端時(shí)是否干凈以利IC運(yùn)作。

在電磁干擾的領(lǐng)域里,信號(hào)路徑一般需注意兩點(diǎn),一是輔助繞組(Vcc)回路,一是小信號(hào)回路。

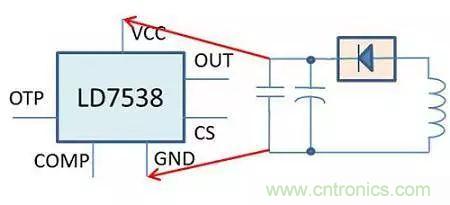

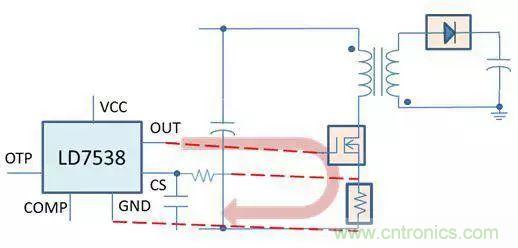

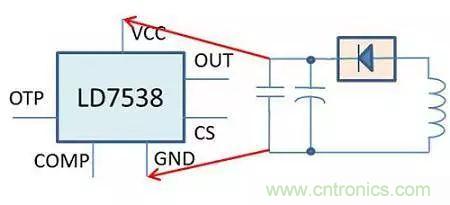

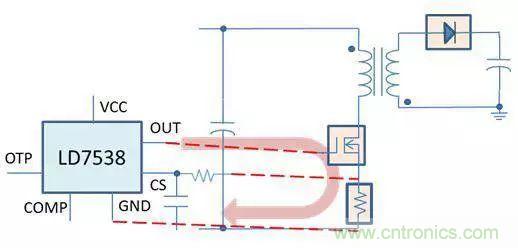

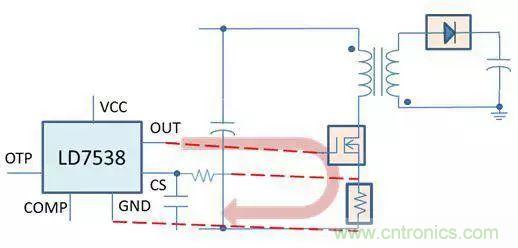

輔助繞組回路如圖24所示,在此舉例的IC為通嘉的6 PIN IC(LD7538),其輔助繞組回路是由變壓器的輔助繞組繞組,二極管,電解電容先形成一開關(guān)回路再接至IC,就如同二次側(cè)的切換回路一般,讓此開關(guān)回路愈短愈好。

IC的供電腳與地腳旁邊通常需并聯(lián)一顆MLCC小電容(0.1uF),此電容愈近IC愈好,因此電容是高頻電容,IC在驅(qū)動(dòng)MOSFET時(shí)會(huì)由此電容抽能量,且其他噪聲在進(jìn)IC前可先被此電容過濾一次,不論此噪聲是經(jīng)由偏壓回路或是地的回路皆有過濾作用。

圖24

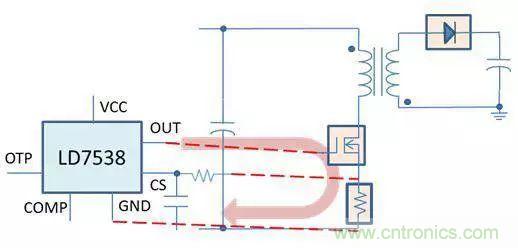

小信號(hào)回路是指IC的各個(gè)出腳端,信號(hào)愈小的腳位愈容易被干擾,IC在運(yùn)作時(shí)不外乎偵測(cè)電壓或電流信號(hào),電壓信號(hào)是由此腳位與地之間形成的電壓準(zhǔn)位來做判定,而電流信號(hào)則是由擷取信號(hào)端到IC腳位上的電流大小來決定,因信號(hào)愈小愈容易被外來的信號(hào)所干擾,尤其是不到1V的電壓信號(hào)或是不到1mA的電流信號(hào),所以在布線時(shí)要非常小心此小信號(hào)的走線。

另外,IC驅(qū)動(dòng)MOSFET的柵極回路里也會(huì)回到IC的地而形成一電源回路,因?yàn)榱藴p少開關(guān)損失,IC流入或流出MOSFET的柵極電流有時(shí)會(huì)超過1A以上,因此IC的輸出至MOSFET的柵極與IC至地的走線也很重要,其回路就如同下圖粉紅色所示。

在此以反激式架構(gòu)來做說明,反激式簡(jiǎn)圖如圖25所示,MOSFET下方會(huì)串聯(lián)一電阻(Rsense)來做電流偵測(cè),其偵測(cè)的信號(hào)通常都很小來達(dá)到低功率損失(<1V),因此布線時(shí)要注意此電阻正端截取的信號(hào)線,若此信號(hào)線在回IC前有加電阻與電容的低通濾波器(RC filter),則此電阻電容要愈靠近IC愈好,如此可讓任何外來的噪聲在進(jìn)IC前皆被此濾波器衰減過,而電阻的負(fù)端(GND)回IC的路徑也是愈短愈粗愈好,因IC是偵測(cè)電阻兩端的電壓來運(yùn)作,路徑愈短可以減少寄生電感的效應(yīng)而讓IC看到愈真實(shí)的信號(hào)。

圖25

因IC的信號(hào)一般都較小,很容易受到外來的干擾而產(chǎn)生誤動(dòng)作,因此在布線時(shí)除了要注意與電源路徑的距離外,也需注意與任何會(huì)產(chǎn)生干擾的組件,像是與磁性組件的磁力線會(huì)影響到的周邊,或是電源輸入線材周邊等高壓電位都是需注意的地方。

電源與信號(hào)路徑有一個(gè)共同接點(diǎn):GND,地的走線對(duì)EMI影響非常大,參考的地回路接線方式如圖26所示。

圖26

橙色線為Y電容建議連接法,讓輸出的地經(jīng)由Y電容直接連至橋式整流器的負(fù)端,讓雷擊或ESD的能量可以快速的經(jīng)由Y電容通過。

綠色線為輔助回路的建議接法,讓電解電容直接回變壓器的地,再單獨(dú)接至大電容的地。

紅色部份為IC的地建議接法,因MOSFET下方的電阻是電源路徑(會(huì)走大電流),要盡量的靠近大電容來形成較小的電流回路,再由大電容拉一條線至輔助繞組的積層陶瓷電容(MLCC),再進(jìn)入IC的地,而其他IC周邊組件的地,即以MLCC電容為中心連接點(diǎn),此接法一般稱為心臟接地,即以此電容為心臟中心,IC周邊下地點(diǎn)都接回至此電容,如此任何的地信號(hào)要進(jìn)入IC的地之前,都可以先被此MLCC電容過濾成較干凈的信號(hào)。

在布線時(shí),任何大面積的導(dǎo)體都需要特別留意,包括散熱片/外殼/輸入/輸出線材等,這些導(dǎo)體如同一天線,會(huì)放大任何在上面的信號(hào),不但這些組件所接的位置非常重要,其經(jīng)過的路徑也需注意;一般來說,散熱片與外殼不可空接,否則其很容易與周邊組件耦合電場(chǎng)效應(yīng)而產(chǎn)生高頻干擾,一般會(huì)使其接一較干凈,在運(yùn)作時(shí)不會(huì)有電位差的電位(GND)。

在此建議的布線方式并不是最好的方式,因不同的變壓器設(shè)計(jì)與布線不同,在EMI里的結(jié)果也會(huì)有差異,有時(shí)必需將干擾源抑制在二次側(cè)或初級(jí)側(cè),有時(shí)則必需將干擾源由Y電容或其他組件導(dǎo)出以得到較佳的EMI,因此在此只提出一個(gè)布線的設(shè)計(jì)參考,使用者在對(duì)策EMI時(shí)仍需做不同的布線方式來得到最佳的EMI效果。

6 EMI濾波器設(shè)計(jì)概念

6.1 基本概念

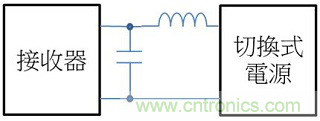

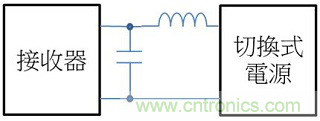

在開關(guān)電源的設(shè)計(jì)里,為了對(duì)策傳導(dǎo)干擾大都會(huì)在輸入端前端加入EMI濾波器,因傳導(dǎo)測(cè)試是由AC端來做量測(cè),因此濾波器愈靠近接收器效果愈好(讓所有的干擾都可經(jīng)由濾波器做衰減),而一般濾波器是經(jīng)由電感與電容組合而成的二階低通濾波器。

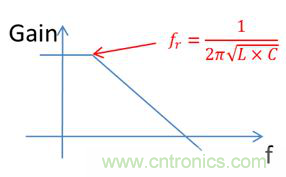

如圖27所示,當(dāng)干擾信號(hào)在經(jīng)過接收器之前,由電感與電容組成的二階低通濾波器來衰減高頻信號(hào),由圖28可知,愈大的濾波電感或電容,可以讓諧振頻率點(diǎn)往前移而衰減更多高頻信號(hào)。

圖27

圖28

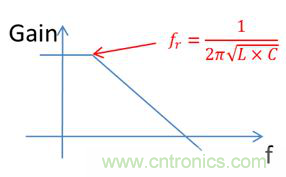

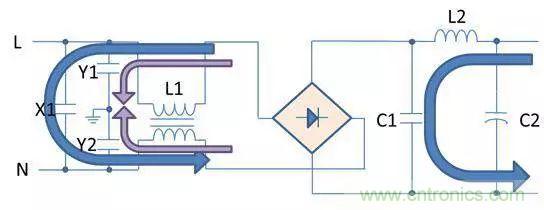

6.2 耦合路徑

在濾波器設(shè)計(jì)上,需確認(rèn)要衰減的路徑是差模還是共模,如圖29所示為常用的EMI濾波電路,藍(lán)色回路為差模濾波器,左邊為L(zhǎng)1與X1,右邊則由L2與C1所組合而成的差模低通濾波器,紫色回路則為共模濾波器,分別由上端的L1與Y1,L1與Y2組合而成。

圖29

6.3 實(shí)際的濾波器考慮

理想的濾波器很容易理解,高頻干擾經(jīng)過低通濾波后衰減其高頻信號(hào)。但在實(shí)際應(yīng)用里,電感或電容愈大,有時(shí)并不一定有較好的EMI效果,甚至有時(shí)還會(huì)較差,這是為什么?

因真實(shí)的電感或電容,必需考慮到組件內(nèi)部的等效電路,像是理想的電容,其阻抗會(huì)隨著頻率增加而減少,但在實(shí)際的電容器內(nèi)部會(huì)有ESL與ESR,當(dāng)頻率與阻抗曲線在超過自諧振頻率點(diǎn)(Fr)之后,其阻抗反而會(huì)因ESL的效應(yīng)而導(dǎo)致頻率愈高,阻抗愈大。

下面就對(duì)濾波電感與電容個(gè)別來做介紹:

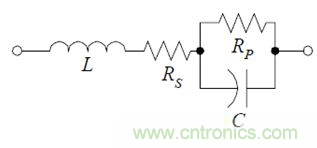

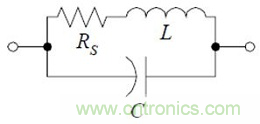

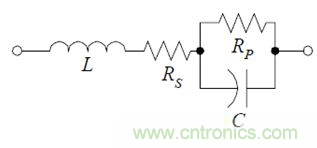

電容:圖30為一電容的等效電路,L為等效電感,Rs為等效串聯(lián)電阻,Rp為等效并聯(lián)電阻,C為其電容值

圖30

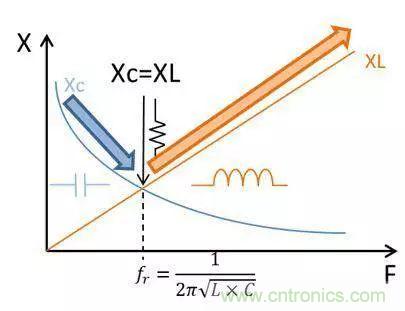

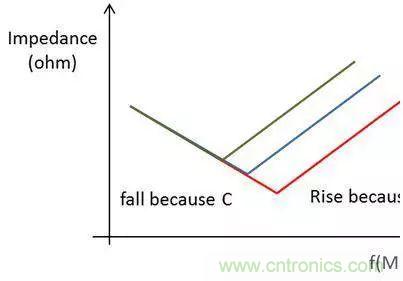

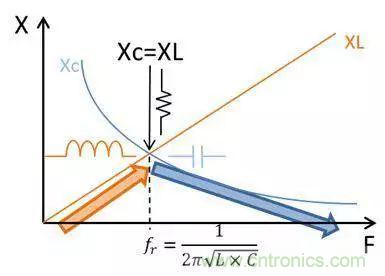

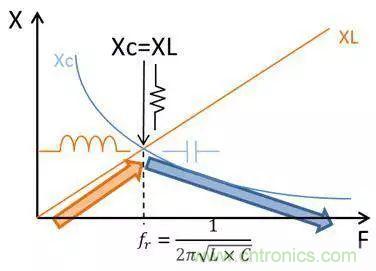

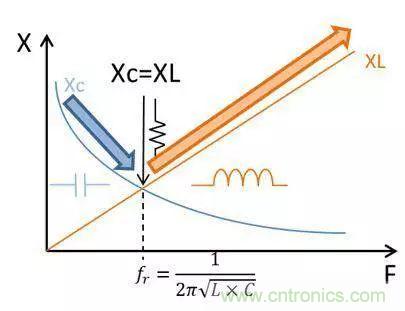

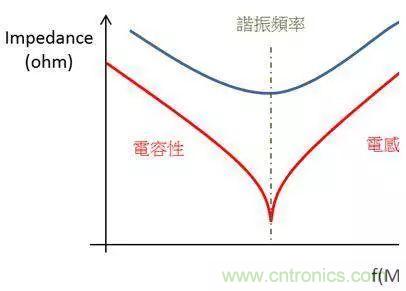

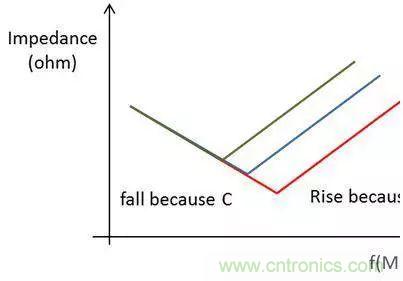

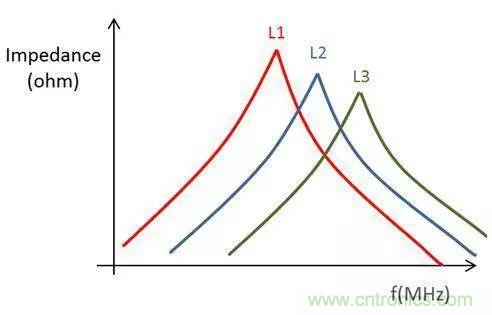

實(shí)際的電容器除了電容值外,仍必需考慮其等效電感與等效電阻的影響,其特性曲線如下圖所示,電容的XL是由其內(nèi)部的ESL所造成,因電容是由二片金屬板繞制而成,因此容值愈大,其ESL也會(huì)愈大,也因此Fr也會(huì)在愈前面,當(dāng)頻率過了Fr后,其阻抗會(huì)由電容性改為電感性。

由圖31的阻抗等效圖可以看出,電容器在低頻時(shí),確實(shí)是由電容所主導(dǎo),頻率增加而阻抗降低,但在過了Fr后,阻抗特性開始由電感(ESL)所主導(dǎo),頻率增加后阻抗反而會(huì)上升,在此頻段的電容呈現(xiàn)一個(gè)電感的特性。

圖31

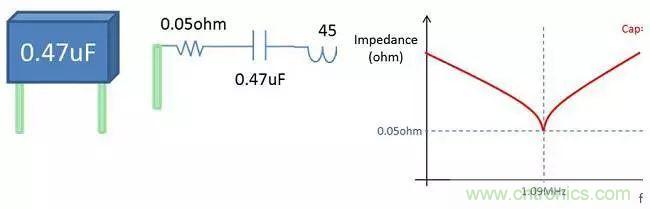

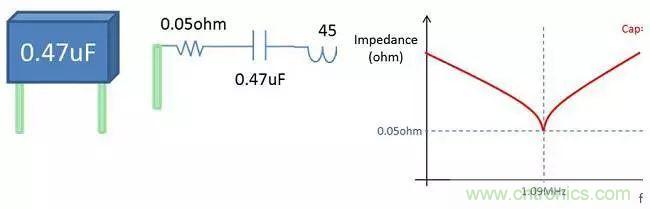

在此舉例一0.47uF的X電容如下圖32所示,左邊為其外型與等效內(nèi)部電路,右邊則為等效內(nèi)部阻抗與頻率曲線圖,量測(cè)得知其等效電感為0.45nH, 等效電阻為0.05ohm,我們可以看出其阻抗在1.09MHz之前是呈電容性下降,在1.09MHz時(shí)呈現(xiàn)急速下降至ESR的位置,并在1.09MHz后呈現(xiàn)電感性上升,轉(zhuǎn)折頻率點(diǎn)為

與圖中轉(zhuǎn)折點(diǎn)相同(此圖為示意圖,詳細(xì)曲線圖請(qǐng)確認(rèn)電容器廠商規(guī)格書或用LCR設(shè)備量測(cè))。

圖32

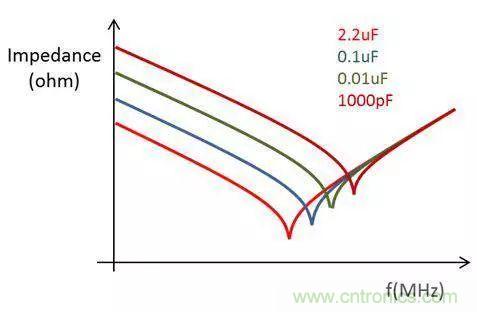

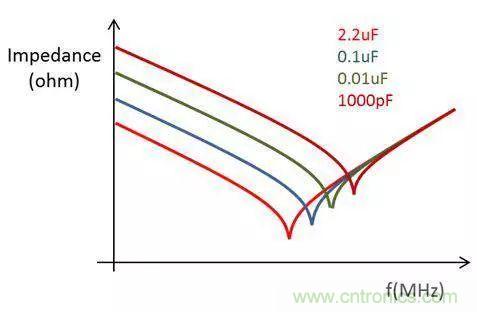

所有的電容其實(shí)都有此頻率特性曲線,像是圖33為一相同類型但不同容質(zhì)所得出的阻抗與頻率曲線,由此圖形可知,不同的容質(zhì)會(huì)因其容質(zhì)與ESL不同而有不同的共振頻率點(diǎn)與與頻率曲線。

圖33

一樣MLCC的電容,也會(huì)因?yàn)槠浣殡娤禂?shù)的不同而影響阻抗特性曲線,如圖34所示為Z5U與NPO(相同容值)所呈現(xiàn)出來的阻抗與頻率曲線。

另外,相同材質(zhì)與容質(zhì),也會(huì)因不同的包裝影響其ESL而有不同的阻抗特性曲線,如圖35為相同容值與材質(zhì),但包裝不同(0402/0603/0805)所呈現(xiàn)出來的阻抗與頻率曲線。

圖34

圖35

由上面的阻抗與頻率特性曲線可得知,在對(duì)策不同頻段的電磁干擾時(shí),必需考慮不同材質(zhì),不同包裝的電容在此頻段時(shí)的阻抗特性為何,并依此來選擇電容器才能達(dá)到預(yù)期的效果。

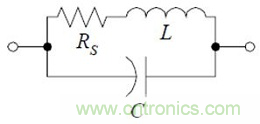

電感:圖36為電感的等效電路,Rs為等效電阻,C為等效電容,L則為其電感量。

圖36

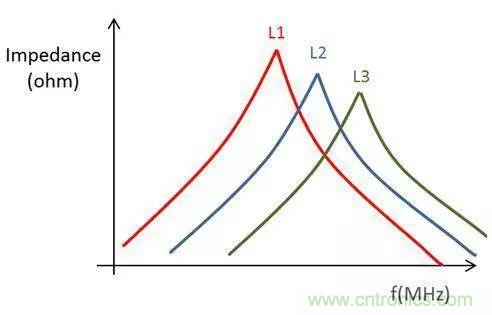

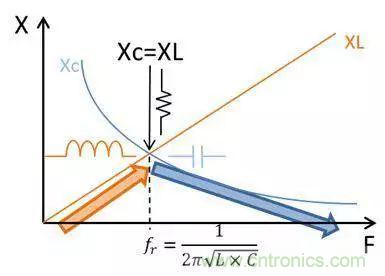

與電容器相似,其頻率特性曲線如圖37所示,在轉(zhuǎn)折頻率點(diǎn)以下時(shí)是由電感所主導(dǎo),但過了轉(zhuǎn)折頻率點(diǎn)之后,會(huì)由電感的等效電容主導(dǎo),當(dāng)頻率愈高時(shí)阻抗反而愈小。感量愈大的電感,因其必需繞制更多圈數(shù)來得到其所需的感量,因此更多的圈數(shù)會(huì)導(dǎo)至更大的寄生電容,轉(zhuǎn)折頻率點(diǎn)也會(huì)較為前面,而在高頻時(shí)的衰減能力也會(huì)較差,如圖38所示為三顆相同環(huán)形鐵心繞制不同圈數(shù)后得出的阻抗頻率特性曲線,L1最多圈因此在前頻段時(shí)上升最快,但也因寄生電容最大而最快被衰減。

另外,電感的等效電容與電感的繞法/圈數(shù)有很大的關(guān)系,一般是圈數(shù)愈多會(huì)有愈大的等效電容,但電感的繞制可以用繞法的不同,像是十字繞法,蝴蝶繞法…等方式,用相同的電感但不同的繞法來得到相同感量但減少其等效電容,藉此來得到較佳的EMI效果。

圖37

圖38

7 變壓器在傳導(dǎo)的設(shè)計(jì)概念

一般工程師對(duì)變壓器的觀念,就是用銅線在鐵粉心的鐵心上繞線,并根據(jù)不同的圈數(shù)與感量,可得到不同的工作周期,電流變化率與MOSFET/DIODE的電壓應(yīng)力;但在EMI的領(lǐng)域里,變壓器的設(shè)計(jì)就沒有這么簡(jiǎn)單,經(jīng)驗(yàn)豐富的工程師都知道良好的變壓器設(shè)計(jì)在EMI里占有舉足輕重的地位,下面就一一來介紹:

7.1 變壓器的基本概念

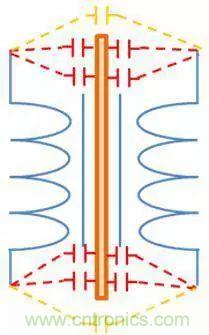

一般開關(guān)電源的變壓器皆是使用鐵粉心(Ferrite Core)制成其鐵心,再由線圈繞制在鐵心上而成,以圖39左邊所示為一線圈繞制在鐵心中間時(shí),因電流在鐵心里所產(chǎn)生的磁通方向。

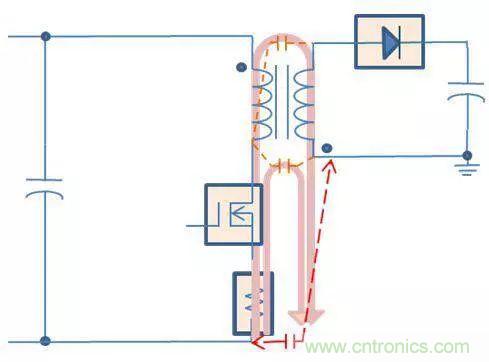

圖39

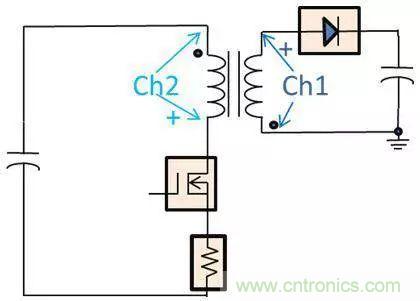

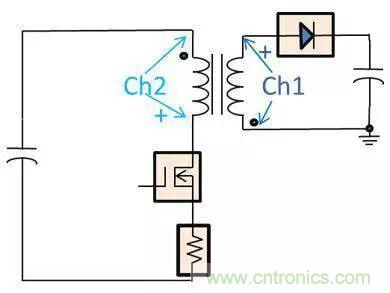

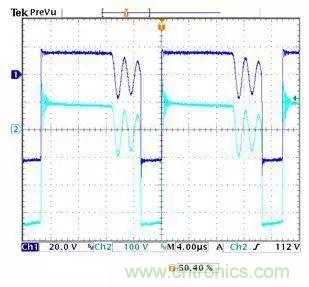

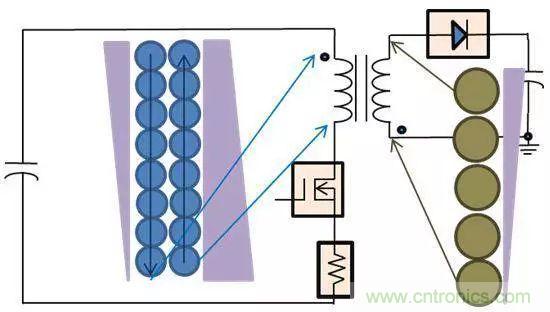

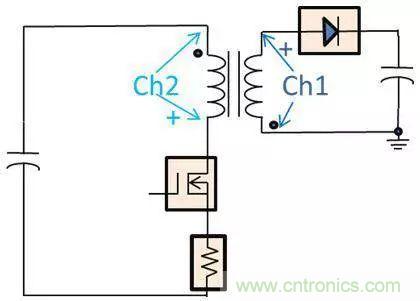

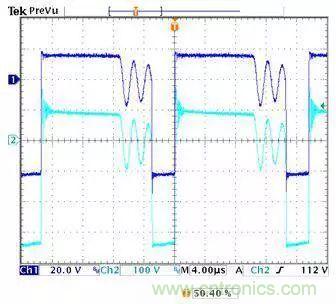

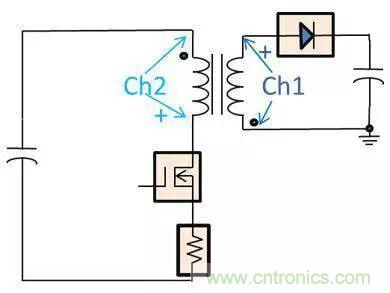

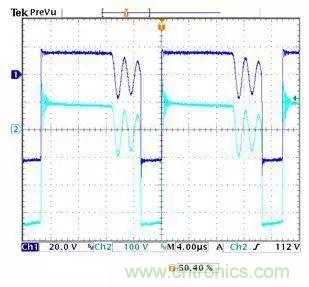

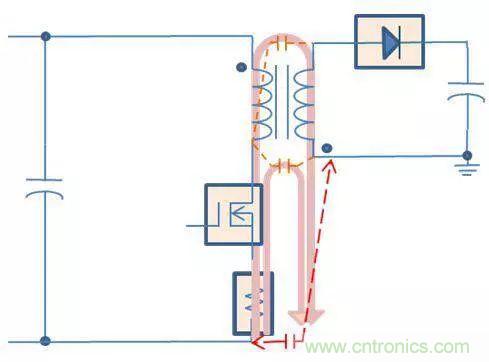

如圖40與41簡(jiǎn)易的反激式線路圖與波形,此為一65W在230V輸入時(shí)的工作情形,量測(cè)變壓器初級(jí)與次級(jí)側(cè)(如圖所示探棒位置),因開關(guān)電源是靠開關(guān)做快速開關(guān)來得到穩(wěn)定的輸出,當(dāng)MOSFET開關(guān)關(guān)斷時(shí),初級(jí)開關(guān)的Drain pin會(huì)由低電壓提升至高電壓,同時(shí)次級(jí)二極管端也會(huì)同樣的由低壓至高壓,但初級(jí)側(cè)電壓的電位差會(huì)遠(yuǎn)高于次級(jí)側(cè)電壓,由之前的觀念可知道,兩導(dǎo)體之間會(huì)有耦合電容,而此電容會(huì)因電位差而產(chǎn)生一電流,如圖42所示,當(dāng)初級(jí)側(cè)導(dǎo)體的電壓高于次級(jí)側(cè)時(shí),將會(huì)有一電流由初級(jí)側(cè)導(dǎo)體經(jīng)由耦合電容流入次級(jí)側(cè)(如綠色箭頭);同理,當(dāng)開關(guān)導(dǎo)通時(shí),初級(jí)與次級(jí)導(dǎo)體的電壓會(huì)由高電壓降低至低電壓,由于初級(jí)側(cè)的電位差比次級(jí)側(cè)較大,因此這時(shí)也會(huì)有一電流由次級(jí)側(cè)導(dǎo)體流入初級(jí)側(cè)(如紫色箭頭)。

圖40

圖41

圖42

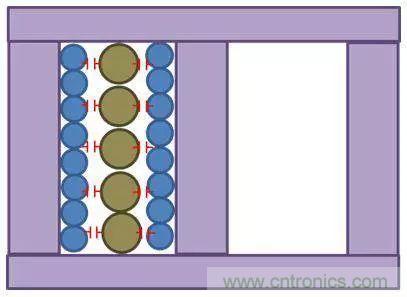

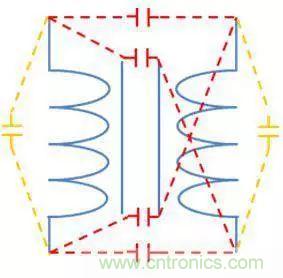

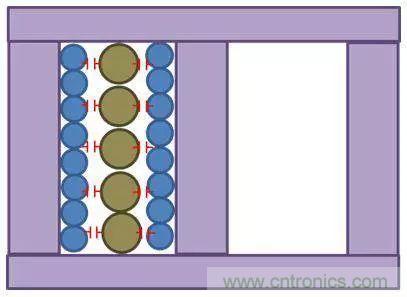

在成型的變壓器鐵心內(nèi)部會(huì)有多數(shù)銅線繞制而成,其結(jié)構(gòu)圖如圖43所示,此為一三明治繞法的變壓器,紫色為變壓器鐵心,藍(lán)色為初級(jí)側(cè)銅線,棕色為二次側(cè)銅線,繞制順序?yàn)椋鹤顑?nèi)層由MOSFET的Drain pin開始由下往上繞,接著再繞二次側(cè),最后再接著初級(jí)的線圈由上往下繞下來,達(dá)成三明治繞法(將二次側(cè)夾在內(nèi)層),但初級(jí)導(dǎo)體與次級(jí)導(dǎo)體之間因距離很靠近,所以在兩者之間會(huì)有耦合電容的產(chǎn)生,就如紅色電容所示。

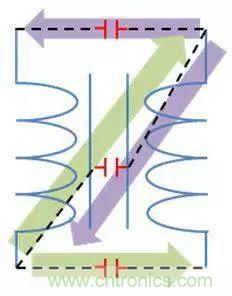

由剛才的波形可得知,MOSFET的Drain pin與二極管的A端是電壓變動(dòng)率最大的地方,而變壓器線圈的另一邊是靜點(diǎn)(因直接連接電容,電壓無法瞬間變化),所以內(nèi)部線圈的電位差是由變化量最大的一端往另一端減小,就如圖44紫色所標(biāo)示一樣,線圈愈靠近MOSFET的Drain pin或是二極管的A端有較大的電位差,而電位差的變動(dòng)量隨著往另一端愈近而愈小。

圖43

圖44

因此在實(shí)際的變壓器繞制上,都會(huì)建議變壓器最內(nèi)層是由電位差變化最大的點(diǎn)開始起繞,讓愈外層的銅線其電位差愈小,如此可讓最內(nèi)層高壓變化的電場(chǎng)被其他相對(duì)電位較小的導(dǎo)體包覆在里面來減低其對(duì)外的輻射效應(yīng)。另外,在做變壓器設(shè)計(jì)時(shí),若一開始就可以考慮此因繞組電位差所導(dǎo)致的電場(chǎng)效應(yīng),將可大大地減少EMI除錯(cuò)時(shí)間。

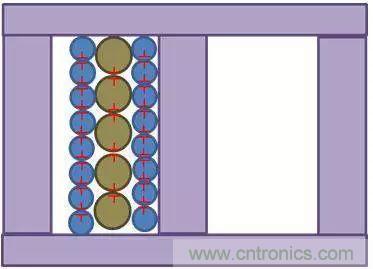

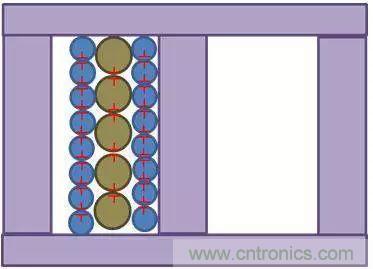

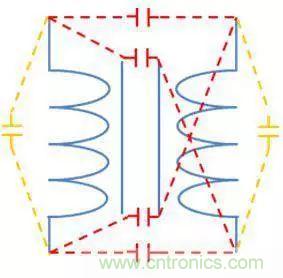

除了介于初級(jí)與次級(jí)側(cè)之間的層間電容之外,初級(jí)側(cè)本身與次級(jí)側(cè)本身之間也會(huì)存在著耦合電容如圖45紅色所示,而在變壓器線路里其等效的寄生電容如圖46所示,紅色為介于初級(jí)與次級(jí)之間,黃色則為初級(jí)本身與次級(jí)本身。此電容量會(huì)隨著圈數(shù)的增加而上升,而此電容量也會(huì)引起高頻電場(chǎng)干擾。

圖45

圖46

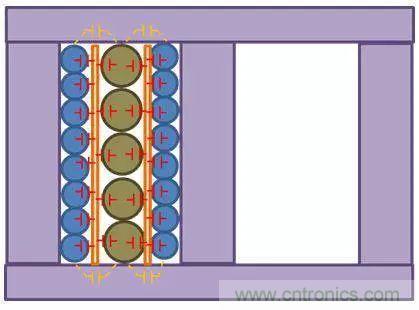

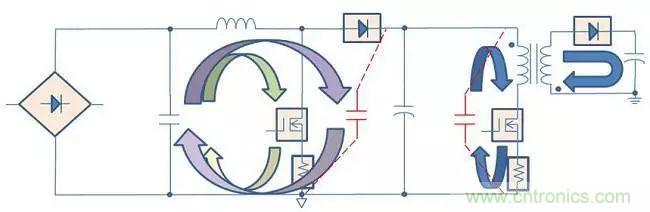

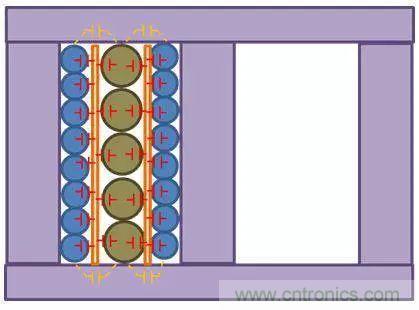

7.2 內(nèi)銅

因介于變壓器初級(jí)側(cè)與次級(jí)側(cè)的耦合電容會(huì)引起嚴(yán)重的電場(chǎng)干擾,因此一般會(huì)在初級(jí)側(cè)與次級(jí)側(cè)之間做電場(chǎng)隔離來減少電場(chǎng)效應(yīng),一般使用的方式是在初級(jí)與次級(jí)之間加一層內(nèi)銅箔或是銅線做電場(chǎng)隔離,如圖47所示為加了銅箔的變壓器,內(nèi)銅箔介在初級(jí)與次級(jí)之間,由高電位差引起的耦合電流大部份會(huì)經(jīng)過紅色的耦合電容至銅箔而形成另一個(gè)回路,大大地減少了耦合至另一側(cè)的耦合電容。

若將此銅箔下PIN回初級(jí)側(cè)(可以是地或是高壓),相當(dāng)于初級(jí)側(cè)產(chǎn)生的高電位差,經(jīng)由電容效應(yīng)到銅箔上,再經(jīng)由銅箔回到初級(jí)側(cè)本身,形成一初級(jí)側(cè)的電流回路,幫助初級(jí)側(cè)電場(chǎng)電流回到初級(jí)側(cè)而做到電場(chǎng)隔離;如此只剩下少部份的如圖48黃色的耦合電容,大大地減少電容效應(yīng)來達(dá)到減少電場(chǎng)干擾的作用。

圖47

圖48

7.3 Y電容

一般在變壓器的初級(jí)與次級(jí)側(cè),我們都會(huì)在兩端的地之間放一顆Y電容,而此Y電容的作用也與上述的一二次側(cè)耦合電容相關(guān);如圖49線路所示,紅色的Y電容介在初次級(jí)側(cè)之間,而初級(jí)側(cè)電壓變動(dòng)所導(dǎo)致的電容效應(yīng),即耦合至次級(jí)側(cè)的電流,可以多了一個(gè)路徑,即經(jīng)由此Y電容回到初級(jí)側(cè),大大的減少共模路徑的干擾。(若沒有此Y電容,則大部份的耦合電流都會(huì)經(jīng)由大地FG回至初級(jí)側(cè))

也因?yàn)閅電容是給予初級(jí)次級(jí)側(cè)一路徑,因此連接的位置與大小也很重要,電容Xc的阻抗為1/2*π*f*c,代表頻率愈高時(shí),其阻抗愈低,高頻信號(hào)愈可以由Y電容流入另一側(cè),但決定的因素卻是因變壓器與布線不同而有不同差異,因?qū)Σ哂袝r(shí)需將干擾源留在內(nèi)部較好,有時(shí)卻是將其流入外部較好,因此不同的案子都必需對(duì)Y電容做些調(diào)整。

圖49

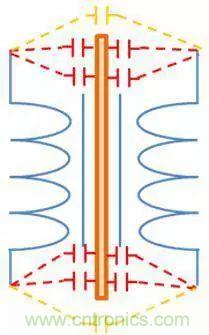

7.4 漏磁

變壓器的漏感(漏磁通)不但會(huì)造成初級(jí)側(cè)開關(guān)Vds過高,也會(huì)對(duì)EMI產(chǎn)生很大的影響。

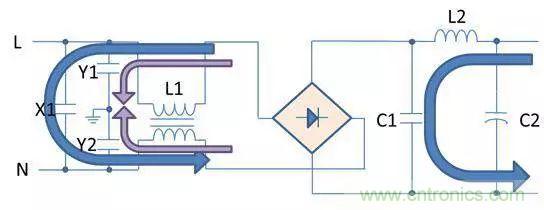

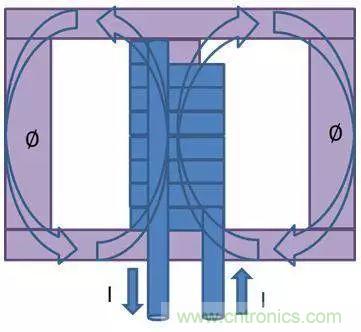

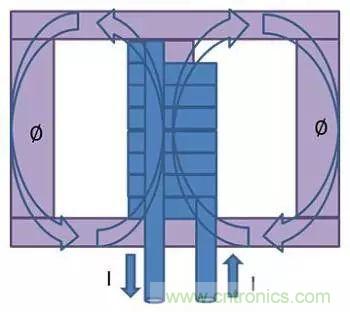

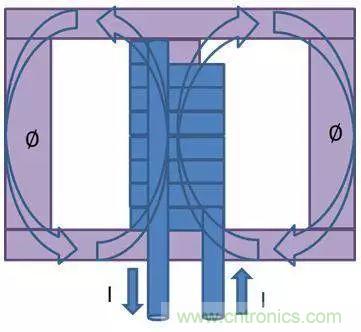

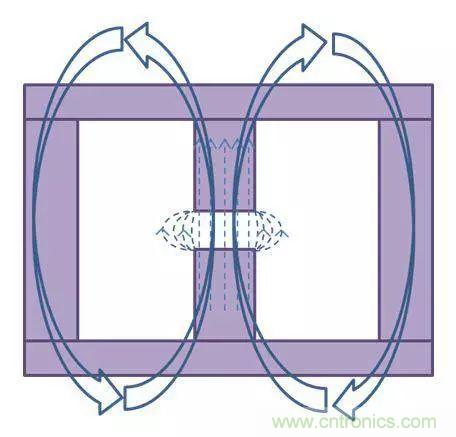

一般開關(guān)變壓器的鐵粉心里都沒有氣隙,因此實(shí)際使用時(shí)都會(huì)因飽和問題而將鐵心磨氣隙,而漏磁最大的地方就在氣隙周邊,在設(shè)計(jì)時(shí)要盡量選擇將氣隙放在變壓器內(nèi)部中心處的鐵心,再用導(dǎo)體或銅箔做屏敝來減低其漏磁的影響,而氣隙中間的漏磁通如圖50虛線所示。

除了氣隙外,雖大部份的磁通會(huì)經(jīng)由導(dǎo)磁路徑(即變壓器鐵心)形成一回路,但仍會(huì)有些許漏磁會(huì)在變壓器外部形成漏磁通,此漏磁通如圖50藍(lán)色箭頭所示,漏磁產(chǎn)生的磁場(chǎng)干擾很容易會(huì)影響周圍的導(dǎo)體或組件。而減少干擾的方法,一是對(duì)變壓器進(jìn)行磁場(chǎng)屏蔽,另一是盡量拉開與變壓器漏磁通之間的距離,或盡量減少在其周邊的電流導(dǎo)體面積。

圖50

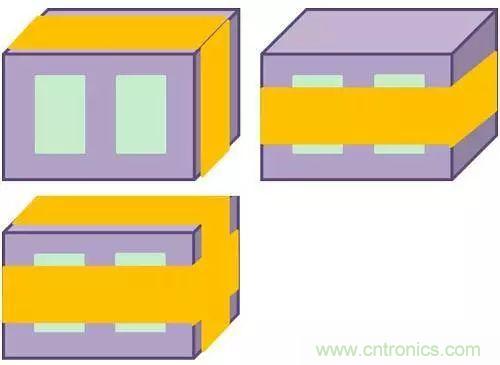

7.5 外銅箔

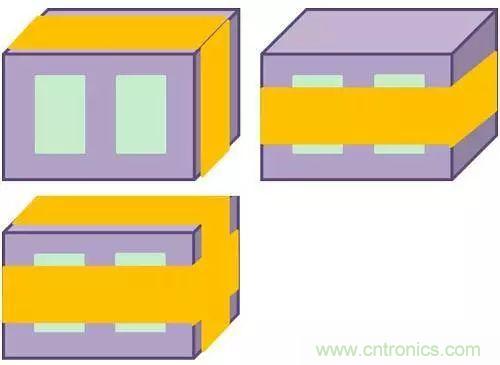

所謂的外銅箔是在變壓器鐵心外圍包覆一銅箔,包覆方式可延著鐵心包覆或是延著線包包覆,也可以同時(shí)包覆鐵心與線包(十字包法),簡(jiǎn)易如圖51所示,左邊為鐵心包覆,中間為線包包覆,右邊則為十字包法,而銅箔兩端接觸后需相連并下地,如此不但可作電場(chǎng)屏蔽也可作磁場(chǎng)屏蔽。

非導(dǎo)磁材料一般是無法對(duì)磁通有屏蔽作用的,但銅箔是良導(dǎo)體,漏磁通穿過銅箔時(shí)會(huì)產(chǎn)生渦流,而渦流產(chǎn)生的磁場(chǎng)正好可抵消變壓器的漏磁通,如此來抑制漏磁所造成的磁場(chǎng)干擾。而銅箔的良導(dǎo)體特性也會(huì)抑制電場(chǎng)耦合效應(yīng),就如內(nèi)銅箔的作用一樣。

圖51

8 對(duì)策EMI——傳導(dǎo)的方法

在做傳導(dǎo)測(cè)試時(shí),可先依下面做些確認(rèn)。

8.1 確認(rèn)測(cè)試方式

首先必需確認(rèn)測(cè)試方式是否正確,不正確的測(cè)試方式會(huì)浪費(fèi)很多時(shí)間,確認(rèn)的地方包括測(cè)試法規(guī)為何/測(cè)試電壓為何(不同國(guó)家有不同電壓輸入)/待測(cè)物是系統(tǒng)或是仿真負(fù)載/系統(tǒng)的工作模式(是否過載或動(dòng)態(tài)負(fù)載)/系統(tǒng)的周邊(monitor,USB或硬盤)是否會(huì)造成干擾源/輸出或電源線是否需下地/外接設(shè)備的地線是否與主電源的地線有分開/是否先空掃一次確認(rèn)接收器的誤差…等等;建議在開始對(duì)策之前,先確認(rèn)以上的測(cè)試環(huán)境是否正確,再開始做對(duì)策;筆者就有過對(duì)策一個(gè)下午后,才發(fā)現(xiàn)其中一項(xiàng)設(shè)定錯(cuò)誤,白白浪費(fèi)一個(gè)下午時(shí)間的經(jīng)驗(yàn)。

8.2 確認(rèn)導(dǎo)體的天線效應(yīng)

任何的導(dǎo)體在測(cè)試EMI時(shí)都會(huì)有天線效應(yīng),因此建議使用客戶量產(chǎn)所用的線材,包括輸入線材與輸出線材(不同的線材會(huì)有些許的差異),而散熱片一般會(huì)下地(或一參考電位),外面有鋁殼或金屬導(dǎo)體時(shí)也要下地,避免導(dǎo)體因電場(chǎng)或磁場(chǎng)效應(yīng)而產(chǎn)生干擾,成品的組件組裝上也需注意是否有遠(yuǎn)離干擾源,任何導(dǎo)體經(jīng)過磁性組件周邊時(shí)也要注意磁性組件漏磁通所帶來的干擾。

8.3 在150KHz~10MHz的頻段一般是由操作頻率的倍頻差模信號(hào)加上共模信號(hào)所組成,一般對(duì)策方式為修改EMI低通濾波器/變壓器耦合路徑/Y電容大小/布線方式等來做對(duì)策,可依文章前面所述方法做確認(rèn)。

9 結(jié)語

電磁干擾(EMI)的防制在電源設(shè)計(jì)里是門很重要的學(xué)問,此篇文章將EMI傳導(dǎo)的法規(guī),量測(cè)法做介紹,并解釋傳導(dǎo)的一些基本概念,包括電場(chǎng)干擾與磁場(chǎng)干擾等,并分析布線,EMI濾波器與變壓器設(shè)計(jì)對(duì)EMI的干擾等。

所有的EMI問題,其實(shí)皆因高速的電壓變動(dòng)所產(chǎn)生的電場(chǎng)干擾,或是高速的電流變動(dòng)所產(chǎn)生的磁場(chǎng)干擾,并搭配組件或布線的高頻路徑(包括寄生電感與電容)所產(chǎn)生,因此只要知道開關(guān)電源的電場(chǎng)與磁場(chǎng)來源,并知道各組件內(nèi)部的等效電路與布線路徑,就可以知道用怎樣的方式可得到較佳的EMI結(jié)果。

推薦閱讀: