【導讀】器件的良率在很大程度上依賴于適當的工藝規格設定和對制造環節的誤差控制,在單元尺寸更小的先進節點上就更是如此。過去為了識別和防止工藝失效,必須要通過大量晶圓的制造和測試來收集數據,然后對采集到的數據進行相關性分析,整個過程費時且昂貴。

通過失效分類、良率預測和工藝窗口優化實現良率預測和提升

器件的良率在很大程度上依賴于適當的工藝規格設定和對制造環節的誤差控制,在單元尺寸更小的先進節點上就更是如此。過去為了識別和防止工藝失效,必須要通過大量晶圓的制造和測試來收集數據,然后對采集到的數據進行相關性分析,整個過程費時且昂貴。如今半導體虛擬制造工具(例如SEMulator3D®)的出現改變了這一現狀,讓我們可以在“虛擬”環境下完成以上實驗。甚至在硅材料中進行工藝實驗之前,虛擬制造就可以用于了解工藝之間的相互影響和工藝步驟靈敏度以實現最大化良率。本文將通過一個簡單示例來演示如何通過虛擬制造來提升7nm節點特定結構的良率,其中使用到的技術包括失效分類、良率預測和工藝窗口優化。

良率提升與失效分類

A.失效分類定義

邊緣定位誤差是導致后段制程良率損失的主要失效模式[1]。下面用簡單實例說明,假設M1由金屬A(MA)和金屬B(MB)組成【通常由LELE(光刻-刻蝕-光刻-刻蝕),或自對準雙重圖形化技術(SADP)工藝產生】,而接觸孔(VC)被設計連接到MB。

金屬關鍵尺寸CD(或SADP工藝中的心軸CD)或VCCD或金屬至VC的套準精度存在工藝誤差,會引起因通孔和金屬層之間產生邊緣定位誤差而導致的良率損失。

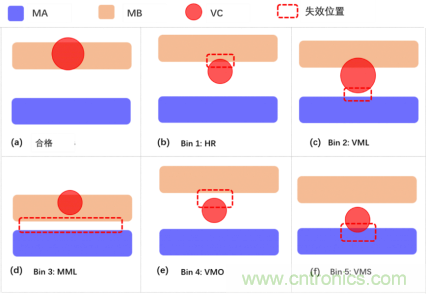

如下失效分類分別對應不同的CD和套準誤差組合(見圖1):

1.高接觸電阻(HR):VC和MB接觸面積過小

2.VC-MA漏電(VML):VC至MA的距離過小

3.MA-MB漏電(MML):MA至MB的距離過小

4.VC-MB開路(VMO):VC未接觸MB,兩者之間沒有重疊

5.VC-MA短路(VMS):VC接觸MA,兩者之間有部分重疊

圖1.分類圖示(a)合格,(b)HR,(c)VML,(d)MML,(e)VMO,(f)VMS

B.結構構建與校準,以及失效模式生成與識別

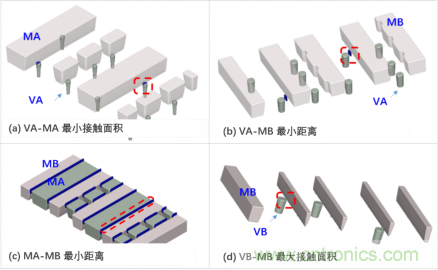

為了演示如何通過虛擬制造提高良率,現構建一個7nm的VC和M1工藝。在生成并校準虛擬工藝結構之后,執行一系列虛擬量測步驟。圖2展示了在虛擬結構上相應的測量位置,根據測量結果,可以將當前失效納入相應的失效分類。

圖2虛擬測量(結構檢索)(a)VA-MA最小接觸面積,(b)VA-MB最小距離,(c)MA-MB最小距離,(d)VB-MB最大接觸面積

基于特定的規格和規則,可以根據測量結果自動實現失效模式分類。

C.良率預測和失效模式排行

在實際的制造過程中,心軸/通孔CD和套準精度等工藝參數被控制在以目標值為中心一定寬度的范圍內分布。通過SEMulator3D可自動執行實驗設計(DOE)并生成和收集由用戶定義的平均值和范圍寬度/標準差。根據收集的數據和預先設定的良率規則,即可計算出合格率或良率(即在特定輸入條件下,通過合格次數與檢驗總次數的比率)。用戶還可以根據生成的測量結果與失效規則做對比,對失效進行自定義分類。

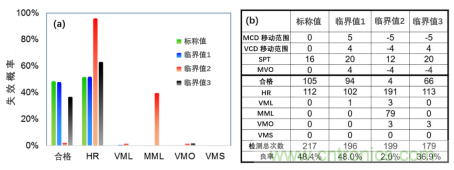

我們首先確定了MCD(心軸CD)、VCD(通孔CD)、SPT(側墻厚度)和MVO(軸心-VCX軸方向套準精度)的均值移動范圍及其分布寬度,之后執行實驗設計,用蒙特卡洛模擬方法執行3000次虛擬實驗測試。圖3(a,b)為四種不同輸入條件下的失效類別匯總條形圖和良率匯總表,通過這些圖表可以看出特定輸入條件下發生各種失效的概率大小并由此判斷出各類失效模式對良率的影響。

圖3.特定MCD/VCD/MVO條件下的良率情況。(a)失效模式條形圖,(b)良率匯總

D.工藝窗口優化

在工藝開發過程中,開展上述分析可能會引發一系列其他問題,例如預測所得的良率是否合理?是否可通過調整規格均值獲得更高的良率?放寬工藝分布寬度要求的同時能否保持良率?如果無法達到滿意的良率結果,是否可以通過收緊分布寬度以達到目標良率,以及收緊程度如何?要回答上述問題就要用到SEMulator3D中的工藝窗口優化(PWO)功能。該功能可以自動搜索具有固定分布寬度的均值組合,然后再根據所收集的數據得出最高良率(合格率)的最佳工藝窗口。

表1所示為工藝參數優化前,優化后,優化后+收緊SPT厚度條件下的良率及其對應的工藝窗口。通過該表可以看出,只需優化工藝規格均值即可將良率從48.4%提高至96.6%,接下來只需進一步收緊SPT分布寬度值即可獲得99%的目標良率。

表1.不同輸入條件下的良率匯總表

結論

本文探討了如何通過虛擬制造提高良率。文中實例采用了因邊緣定位誤差導致VC-M1良率損失的7nm6TSRAM模型,采用的技術包括結構構建、模型校準、虛擬量測、失效分類、良率預測和工藝窗口優化。分析結果表明通過工藝窗口優化功能和收緊規格要求可以將良率從48.4%提高到99.0%。可以看出,虛擬制造可廣泛應用于各種良率提升研究,而這些研究的結果將推動半導體工藝和技術的發展。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請電話或者郵箱聯系小編進行侵刪。