【導(dǎo)讀】如今的集成電路 (IC) 與二十多年前的集成電路有著天壤之別。新一代的芯片面積更小,但集成了盡可能多的功能,采用了先進(jìn)的處理節(jié)點和獨特的架構(gòu),以實現(xiàn)整個芯片的高能效信號傳輸。摩爾定律所涉及的不僅是晶體管柵極尺寸變小,也涵蓋了低功耗架構(gòu)。

本文要點

超大規(guī)模集成電路 (Very large scale integration,VLSI) 是一種主流的集成電路 (IC) 設(shè)計模式。

芯片尺寸微型化有助于降低單個晶體管的功耗,但同時也提高了功率密度。

先進(jìn)封裝的低功耗設(shè)計趨勢勢頭未減,而更新的技術(shù)有助于在不犧牲計算性能的情況下降低器件的功耗。

如今的集成電路 (IC) 與二十多年前的集成電路有著天壤之別。新一代的芯片面積更小,但集成了盡可能多的功能,采用了先進(jìn)的處理節(jié)點和獨特的架構(gòu),以實現(xiàn)整個芯片的高能效信號傳輸。摩爾定律所涉及的不僅是晶體管柵極尺寸變小,也涵蓋了低功耗架構(gòu)。

隨著電子產(chǎn)品的尺寸不斷微型化,芯片設(shè)計人員需要考慮采用新的方法來實現(xiàn)和擴(kuò)展低功耗設(shè)計技術(shù)。用于數(shù)據(jù)中心、人工智能、視覺和許多其他應(yīng)用的處理器性能強(qiáng)大,集成的功能也越來越多,因此預(yù)計 VLSI 設(shè)計的功率密度也會增加。低功耗設(shè)計技術(shù)和新技術(shù)可以應(yīng)對總功耗增加的挑戰(zhàn),確保新產(chǎn)品性能可靠,并支持?jǐn)U展到更小的技術(shù)節(jié)點。

即使采用了低功耗設(shè)計工藝,GPU 仍會嚴(yán)重發(fā)熱

功耗的主要方面

許多先進(jìn)集成電路(如專用 SoC 和通用處理器)中使用了較新的芯片架構(gòu),需要在裸片上集成更多的功能,因此需要增加硬件驅(qū)動的電源管理功能。實施低功耗設(shè)計技術(shù)的目標(biāo)主要是延長電池壽命(移動設(shè)備)、減少發(fā)熱(所有其他設(shè)備)或兩者兼顧(智能手機(jī)和其他移動設(shè)備)。VLSI 設(shè)計中的低功耗設(shè)計技術(shù)一般在兩個方面進(jìn)行功耗優(yōu)化:

1.動態(tài)功耗

動態(tài)功耗是指工作過程中消耗的電量。更具體地說,動態(tài)功耗是在邏輯電路切換狀態(tài)時,晶體管結(jié)構(gòu)中電容充放電時消耗的總電量。CMOS 邏輯電路只在開關(guān)時消耗電量,因此減少開關(guān)事件的次數(shù)和導(dǎo)通電壓有助于降低設(shè)備的總功耗。

2.靜態(tài)功耗

靜態(tài)功耗是工作電壓和漏電流的乘積。即使晶體管處于關(guān)斷狀態(tài),也會有一些電流通過柵極泄漏,以熱量的形式散失。與早期的雙極設(shè)計相比,CMOS 芯片架構(gòu)的漏電流更低,但規(guī)模擴(kuò)展給保持低漏電流帶來了挑戰(zhàn)。

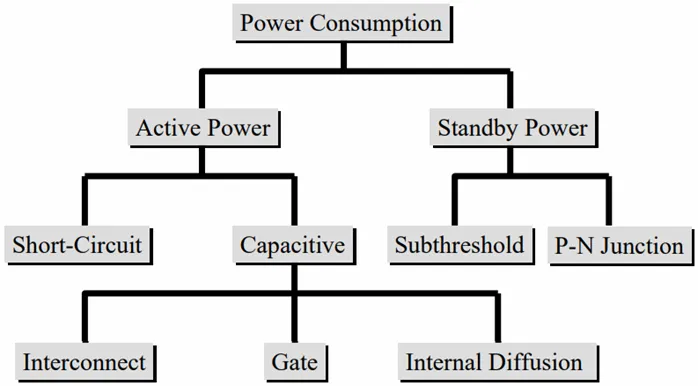

下圖展示了集成電路在運(yùn)行和睡眠/待機(jī)模式下產(chǎn)生功耗的一些區(qū)域和工作模式:

VLSI 電能耗散和損耗的來源

降低以上功耗主要針對靜態(tài)和動態(tài)功耗,但隨著器件規(guī)模的擴(kuò)大,還需要調(diào)整晶體管和互連的結(jié)構(gòu)。我們在這方面取得了一些進(jìn)展,其中最主要的是使用具有高介電常數(shù) (high-k) 的 FinFET,以確保在開關(guān)過程中更完整地調(diào)制到導(dǎo)通狀態(tài),并通過單一解決方案降低漏電流。對于更新的技術(shù),需要利用類似的創(chuàng)新晶體管架構(gòu)和新材料來實現(xiàn)進(jìn)一步擴(kuò)展。除了簡單的架構(gòu)擴(kuò)展外,一些晶片上硬件方法也可用于降低功耗。

主要的低功耗設(shè)計技術(shù)

經(jīng)過 30 多年的發(fā)展,出現(xiàn)了一些解決方案。最初,擴(kuò)展帶來了更低的功耗和更高的功能密度,但最終,時鐘擴(kuò)展增加了功率密度,因此亟需新的技術(shù)。如今,集成電路中使用的低功耗設(shè)計技術(shù)主要包括:

動態(tài)電壓縮放

邏輯電平的電壓可根據(jù)需要升高或降低,以控制功耗。降低邏輯電平可降低開關(guān)時的功耗。

動態(tài)頻率縮放

系統(tǒng)時鐘的時鐘頻率和邊沿速率可根據(jù)需要上下調(diào)節(jié)。

時鐘門控

用于切斷某些邏輯塊的系統(tǒng)時鐘,防止不處理數(shù)據(jù)的邏輯電路進(jìn)行開關(guān)操作。

基板偏置控制

與電壓縮放配合使用,控制構(gòu)成邏輯電路的 MOSFET 進(jìn)入線性區(qū)或飽和區(qū)的閾值。該技術(shù)有時也稱為反向偏置,即在 CMOS 緩沖器的基板區(qū)域施加電壓,以提高或降低邏輯狀態(tài)閾值電壓并減少漏電流。

應(yīng)用這些主動縮放機(jī)制時,并不一定需要修改邏輯電路中晶體管的結(jié)構(gòu),不過為此確實需要添加額外的控制電路,以便根據(jù)某些邏輯條件進(jìn)行縮放。

新產(chǎn)品可能需要采用獨特的架構(gòu)

以上列出的低功耗設(shè)計技術(shù)是設(shè)計新型專用集成電路 (ASIC) 的起點,面向人工智能、量子、視覺/圖形和異構(gòu)集成系統(tǒng)等高級應(yīng)用。對于支持上述應(yīng)用的通用處理器,也應(yīng)繼續(xù)使用同樣的技術(shù)。然而,特定應(yīng)用領(lǐng)域的計算工作負(fù)載更高,因此功耗更低的高度專業(yè)化處理器架構(gòu)更加受到青睞。這方面的例子包括:

以最少的邏輯運(yùn)算執(zhí)行高效張量運(yùn)算的 AI 優(yōu)化芯片。

可針對特定的高計算工作量對其邏輯塊進(jìn)行高度定制或并行化的 FPGA。

包含專用 DSP 塊的語音和視覺處理器。

異構(gòu)集成是將這些功能整合到單一封裝中的一種設(shè)計模式,迫使半導(dǎo)體電源管理工程師采用系統(tǒng)級方法進(jìn)行低功耗設(shè)計。

尤其是,人工智能是當(dāng)下的計算范式,它推動了一類新型低功耗 ASIC 的高效張量運(yùn)算。為了讓這些先進(jìn)產(chǎn)品實現(xiàn)低功耗,涉及到的挑戰(zhàn)之一是完全重新設(shè)計晶體管架構(gòu),以減少執(zhí)行人工智能工作負(fù)載所需的開關(guān)事件數(shù)量和邏輯狀態(tài)變化。最新的設(shè)計采用單晶體管模擬計算方法來實現(xiàn)片上神經(jīng)網(wǎng)絡(luò),完全不需要邏輯塊來運(yùn)行這些計算。其他先進(jìn)技術(shù)、材料平臺和混合信號設(shè)計方法可在專用集成電路和通用處理器中實現(xiàn),因而可以隨著功能密度的提高,繼續(xù)推動低功耗計算。

借助業(yè)界一流的 VLSI 設(shè)計軟件和系統(tǒng)分析工具,您可以輕松構(gòu)建、仿真和評估您的設(shè)計,最大限度地降低整個系統(tǒng)——而不僅僅是 CPU 內(nèi)核——的功耗。如果您需要在物理 layout 中實現(xiàn)低功耗設(shè)計,Cadence Sigrity X 工具套件可以助您一臂之力——新一代 Sigrity 解決方案重新定義了 SI 和 PI 分析,將性能提高了 10 倍,同時保持了 Sigrity 工具一貫的準(zhǔn)確性;不僅配備了強(qiáng)大的系統(tǒng)級分析仿真引擎,旗艦產(chǎn)品 Cadence Clarity 3D Solver 更采用了創(chuàng)新的大規(guī)模分布式架構(gòu),同時與 Cadence Allegro X PCB Designer 和 Allegro X Advanced Package Designer 緊密集成。

這一全新特性可以幫助 PCB 和 IC 封裝設(shè)計師將端到端、multi-fabric和多電路板系統(tǒng)(從發(fā)射端到接收端或從電源到耗電端)相結(jié)合,確保 SI/PI 成功簽核。

文章來源:Cadence楷登PCB及封裝資源中心

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請聯(lián)系小編進(jìn)行處理。

推薦閱讀:

半導(dǎo)體后端工藝|第九篇:探索不同材料在傳統(tǒng)半導(dǎo)體封裝中的作用