【導讀】提出了一種線性化級聯組合信號IC的新方法,用于原位校正PCB缺陷和相互加載。這樣可以大幅縮短系統設計/原型設計周期,并以可忽略不計的功耗成本最大限度地提高信號鏈性能。報告了使用高達3GHz的RF信號并使用12b/10GSPS ADC進行的實驗結果,驗證了該方法的有效性。

提出了一種線性化級聯組合信號IC的新方法,用于原位校正PCB缺陷和相互加載。這樣可以大幅縮短系統設計/原型設計周期,并以可忽略不計的功耗成本最大限度地提高信號鏈性能。報告了使用高達3GHz的RF信號并使用12b/10GSPS ADC進行的實驗結果,驗證了該方法的有效性。

介紹

基礎設施通信系統、儀器儀表和防空應用的進步推動了對RF和混合信號IC的更高性能要求,特別是高速/高動態范圍數據轉換器[1-3]。

然而,在信號鏈中的IC之間插入的印刷電路板(PCB)和封裝會引入寄生效應,并遭受制造缺陷的影響,從而導致網絡中的電路不平衡并損害GHz信號的線性度。

模數轉換器(ADC)的采樣保持放大器(THA)前面通常有一個片內緩沖器,以簡化與片外驅動放大器(或可變增益放大器)的耦合。片上緩沖能力有限,耗電大,并且在高頻時會減弱。IC之間的相互加載引入了額外的非線性或改變IC最佳工作條件。

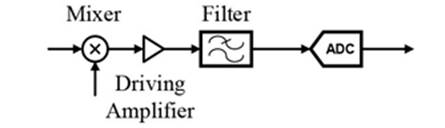

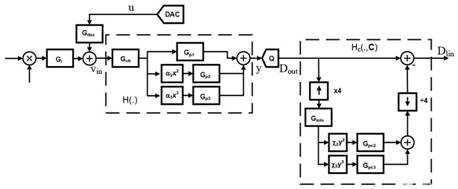

接收(Rx)信號鏈如圖1所示。每個功能模塊(混頻器、驅動放大器、濾波器和ADC;后者包括前端緩沖器和THA)是同一PCB上的獨立IC。雖然每個模塊都可以單獨(或在實驗室的最佳定制板上)發揮最佳性能,但一旦耦合并受到雜散和實際PCB的限制,整個鏈的凈性能可能會受到限制。

數字。1. 經典“接收”(Rx)信號鏈示例。

IC設計人員努力加強芯片接口的電路,以滿足在各種負載條件下所需的性能。通常,使用這些組件的系統設計人員需要定制和迭代設計,以最大程度地減少上述損傷的影響。IC高級模型(通常是簡單的電子表格)的局限性和電路板雜散建模不足加劇了這種努力。原型設計工作可能會為高性能系統的開發增加幾個月的時間,并且需要IC供應商的應用工程人員的參與[4,5]。

這里介紹的非線性校準(NLC)方法通過在寬輸入頻率范圍內校正動態非線性失真來緩解這些問題。RF/混合信號IC整個信號鏈的非線性模型的參數是原位確定的,即在系統板上確定。然后推導一個數字逆校正函數,使二階和三階失真為零。這是在信號鏈處理信號之前在前臺執行的。然后,逆函數實時應用于ADC輸出端的數據流,從而對損傷的影響進行后失真(線性化)。這讓人想起數字預失真(DPD)或通信系統中的回聲/傳輸消除[6]。

本文的組織結構如下。第二部分討論校準系統及其操作。第三部分介紹了非線性、模型參數識別和二次和三次諧波失真的消除所采用的模型。最后,第四部分報告了實驗結果,量化了所提出的校準的有效性。

信號鏈的非線性消除

背景

假設圖1中的每個IC(例如驅動放大器、濾波器、ADC)都已經過單獨優化。因此,例如,如果ADC需要內部前臺校準[3],則需要事先完成。

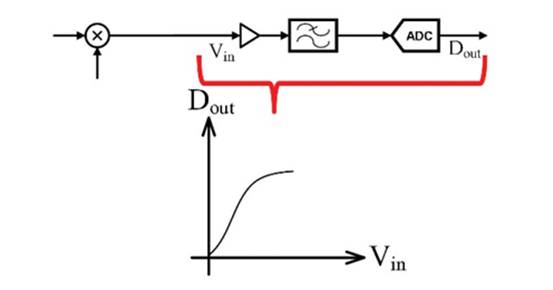

然后,我們考慮ADC數字輸出之間存在的凈靜態非線性特性,例如,ADC的數字輸出之間D外和驅動放大器的模擬輸入v在如圖 2 所示。圖2的下部勾勒出卡通曲線(為了解釋而夸大)。這捕獲了由各種損傷引起的整體非線性,例如放大器和抗混疊濾波器之間以及濾波器和ADC輸入之間攜帶差分模擬信號的成對走線之間的殘余不平衡,加上所有雜散,以及模塊之間的相互負載等。

數字。2. 信號鏈非線性。

為了理解這一點,我們考慮一下,例如,僅ADC的低頻線性度通常優于75dB,即優于5000分之一。無論ADC性能如何,任何電路板設計缺陷或隨機制造缺陷,如果不是明顯好于此缺陷,都會影響和降低信號鏈的凈線性度。更糟糕的是,在處理GHz范圍內的寬帶信號的應用中,如基礎設施通信系統或高性能儀器[6],這種非線性也具有頻率相關分量,因此其行為無法僅使用泰勒級數展開進行精確建模。

算法線性化的操作

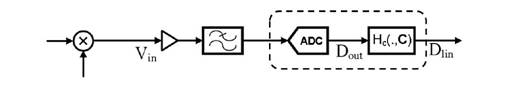

假設信號路徑非線性是弱單調非線性[6,7]。設 H(.) 是D外和v在如圖2所示。所提出的消除方法包括通過應用反函數以數字方式反轉其失真Hc(.)到ADC的輸出數據流D外,返回線性化數據流D林如圖 3 所示:

![]()

其中 G 和D0分別是轉換增益和失調。Hc(.) 嵌入在 ADC 中,由表示轉換器芯片的虛線表示。

數字。3. 非線性度的數字校正。反函數 Hc(.)嵌入在 ADC 中(虛線勾勒出芯片)。

Hc(.)其特征在于由向量C捕獲的許多模型參數。下面概述了原位確定C的程序。

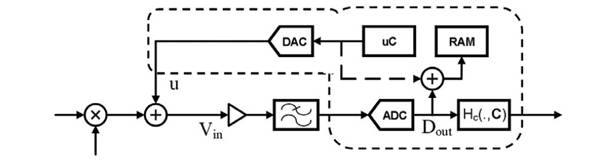

為此,H(.) 需要使用施加的信號來執行。這是在信號鏈工作之前完成的,沒有混頻器輸出。在驅動放大器的輸入端生成并注入測試信號u。u由數模轉換器(DAC)合成,該轉換器也與ADC位于同一芯片上,如圖4所示,但集成不是必需的。DAC線性度需要優于目標信號路徑線性度。微控制器uC還嵌入在ADC中,以執行多種功能,包括ADC本身的初始校準[3],此處用于控制和執行模型識別算法和反函數創建。

數字。4.注入測試信號。

模數轉換器輸出D外對應于由H(.)處理的信號U的數字表示存儲在片上RAM上。在此之后,u 歸零,RAM 的內容由 uC 處理以估計 C,從而確定Hc(.,C) 如圖 5 所示,稍后將對此進行詳細說明。

數字。5.校正參數的確定。

一旦找到C,信號鏈就可以以實際v在,現在是混頻器的輸出,并返回線性化輸出D林(因為 Hc(.) 使鏈失真無效)。從這一點開始,C沒有變化。如果工作溫度或其他參數漂移重新出現過度失真,則需要重新校準[9]。

所提出的方法是可擴展到功能更多的塊。例如,還可以包括驅動放大器前面的混頻器。為此,用于注入u的求和節點在圖5左側的混頻器信號輸入處向上游移動。施加u時,另一個混頻器的端口需要用本地振蕩器激勵,但在此校準階段,沒有其他RF信號施加到混頻器的Rx輸入。該過程在概念上與前面描述的過程相同。

建模、刺激和校正

建 模

H(.) 及其逆模型類型所采用的模型類型Hc(.)是一個平行的、時間離散的哈默斯坦模型[8],由平行分支組成,每個分支包含一個靜態非線性元素,后跟一個動態線性元素。這種選擇是合理的,因為非線性的主要來源的性質是連續時間驅動放大器、濾波器、緩沖器等[6,7]。當其他非線性源(如時間交錯失真或采樣電荷注入失真)先前可以忽略不計時,這是有效的[1-3,9]。

圖 5 鏈的完整動態模型如圖 6 所示。所有具有傳遞函數 G 的模塊都是線性濾波器。例如,理想的DAC輸出u可以由傳遞函數線性頻率塑造G發援會,通常可能與傳遞函數不同G我來自混頻器的射頻輸出。H(.) 的模型由線性分量、二次分量和立方分量組成,每個分量都有線性濾波器。理想量化器Q返回數字輸出D外頻率采樣fs.

圖6.鏈的完整模型,包括 H(.) 和 HC(.)。

D外然后由Hc(.,C),它也使用哈默斯坦模型,其中輸入信號的二次分量和三次分量被估計、組合并從失真序列中減去D外返回更正的序列D林.Hc(.,C) 中的函數系數構成 C,這些系數可以直接與 H(.) 中的系數代數相關。

而v在假設始終處于第一奈奎斯特波段(輸入頻率f在假定為f在C 的訓練算法中產生了歧義,并且還需要分別估計二次項和三次項的傳遞函數響應,并分別估計第二和第三奈奎斯特區。校正中的歧義已在 H 中得到解決C通過引入足夠高的插值,在我們的例子中為 4x,在二次和三次校正項的求和之前(隨后在應用校正之前被抽取 4)。

刺激和模型識別

DAC和ADC均以速率計時fs.寬帶偽隨機序列以及單音和雙音都被用作刺激來訓練系數C并導致可比較的結果,盡管這兩種方法中的每一種都有自己的優點和缺點。在本文的其余部分,僅討論了單音調刺激的情況。

在這種情況下,DAC 將 u 合成為形式為 cos(ωt + ?0).產生多個頻率ω的音調,確保產生的諧波不會相互疊加混疊(即在采樣時,這些諧波不會落在相同的頻率箱中)。

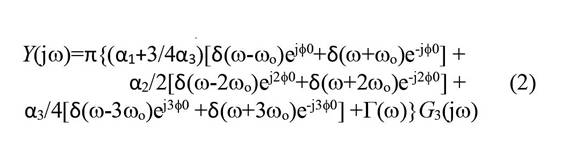

使用比圖 6 所示更簡單的 H(.) 模型,為了簡化數學運算,理想采樣器/量化器 Q 之前的失真信號 y(t)可以寫為 y(t) = [α1v在(t) + α2v在2(t) + α3v在3(t)] *g3(t) 凡α2和α3是失真系數,非線性項與線性時不變(LT I)脈沖響應復雜g3更正D外的訓練算法Hc需要估計α2, α3和g3(t)。

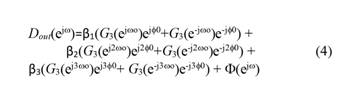

y 的傅里葉變換為:

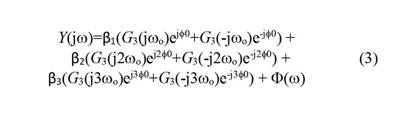

其中 Г(ω) 包含一些其他(交叉)項,而不是ωo, 2ωo或 3ωo.這可以寫成:

其中 ?(ω) 包含一些其他不在ωo, 2ωo或 3ωoα和β可以相互關聯。因為D外是 Y 的數字表示,因此:

由H(.)產生的基波、二次和第一次諧波,標度和相移G3很容易看到。這些術語映射到Hc取消二次項和三次項。因此,C 可以從 H(.) 計算出來。反過來,H(.)可以從其通過以均勻間隔的頻率注入音調u獲得的頻率響應中識別出來,如第II節所述,避免主諧波落在相同的FFT箱上。然后,如所見,C 是代數找到的。

(4)上的更多代數表明,當二階和三階諧波D外別名到第一奈奎斯特帶,(4)中的相應項被相位否定,這需要跟蹤。此外,而不是提取β2G3(eJωo), β3G3(eJ3Ωo)在(4)中,它們與β的關系1G3(eJωo)實際使用,因此僅在第一奈奎斯特區需要激勵,但需要更多計算。如果G發援會是一個一階系統,它的影響可以通過了解的力量來解釋D外的根本。最后,將DAC定時于以下位置引入的另一個實際限制fs如f在接近奈奎斯特,是u將是sinc形的,更重要的是u的(fs–f在) 第一個圖像也接近奈奎斯特并產生光譜估計問題。

實驗結果

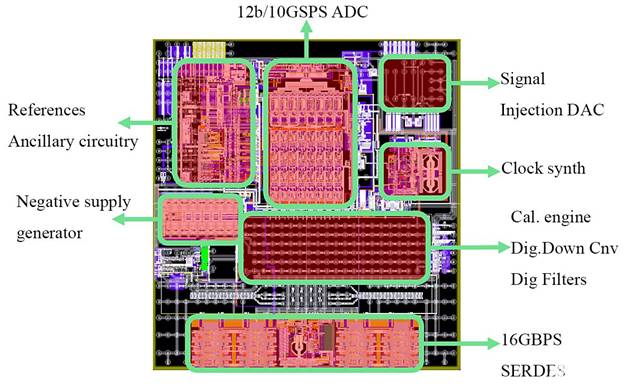

NLC已應用于信號鏈,如圖2所示,并使用圖7所示的芯片,嵌入[3]中所述的12b/10GSPS ADC、14b/10GSPS信號注入DAC、10GHz低相位噪聲時鐘合成器、校準引擎(包括微控制器uC)和本文范圍之外的其他功能,例如數字下變頻器和濾波器。此處報告的結果是在采樣率fs=6GSPS,這是射頻信號接近3GHz的通信系統所要求的[6]。

數字。7.芯片的芯片布局和主要功能塊。

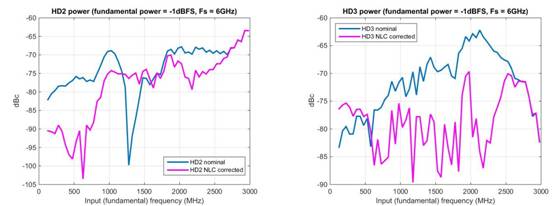

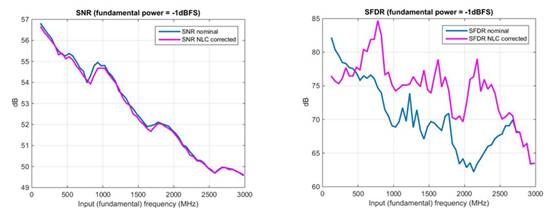

在對近滿量程激勵進行線性化之前,已經測量了信號鏈的單音次級(HD2)和三次諧波(HD3)失真性能、信噪比(SNR)、無雜散動態范圍(SFDR)和雙音三階交調失真(IMD3)。結果在圖8-11中標記為“標稱”的曲線中報告。

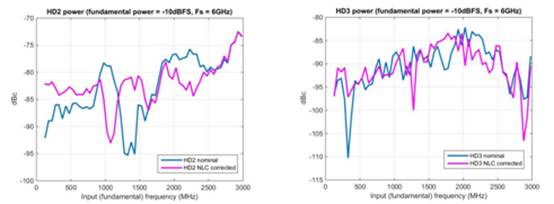

數字。8. (a) HD2 和 (b) HD3 與 f 的單音失真性能在線性化之前(標稱)和線性化后(校正)的基波輸入功率為 -1dBFS 和 fs=6GSPS。

數字。9. (a) 信噪比和 (b) SFDR 與 f在對于 -1dBFS 和 f 的輸入s=6GSPS。

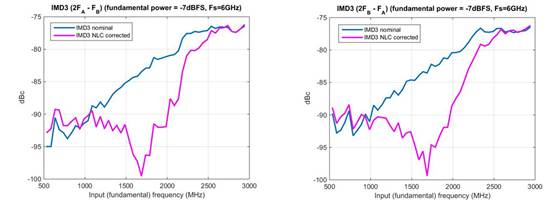

數字。10. 雙音IMD3 for (a)(2F)一個–Fb) 及 (b)(2樓)b–F一個)與 f在= (F一個+Fb)/2 表示 –7dBFS 和 f 的輸入s=6GSPS。

數字。11. (a) HD2 和(b) HD3 與 f在適用于 –10dBFS 和 f 的小輸入s= 6GSPS。

然后應用 NLC,再次測量性能指標,并在標記為“NLC 校正”的疊加曲線中以相同的數字報告。在NLC之后,線性度性能在幾乎整個奈奎斯特范圍內顯著改善,最終隨著輸入接近而達到遞減的回報fs/2,如預期的那樣。圖10a顯示噪聲性能(SNR)沒有像預期的那樣受到影響。圖10b中SFDR的改進證實了HD2和HD3的主要貢獻,驗證了對模型選擇所做的假設。

雖然這些曲線顯示了接近滿量程(-1dBFS)激勵的系統性能,但重要的是要確認NLC適用于較小的激勵。因此,無需重新校準,而只需減少v在的功率,失真已在較低的輸入功率電平(即-3dBFS,-6dBFS,-10dBFS)下重新測量。由于空間限制,圖11中僅報告了-10 dBFS的更極端情況。雖然由于激勵較小,標稱性能在前期有所改善,但除了低頻時HD2略有下降外,NLC性能優于或與標稱性能相當,證實了該方法的魯棒性。

在實時運行的校準鏈中,數字逆函數的應用僅增加了約150mW的功耗,而整個信號鏈消耗的總功耗超過5W,無需校正。

(作者:Nevena Rakuljic, Carroll Speir, Eric Otte, Jeffery Bray, Corey Petersen, and Gabriele Manganaro)

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理。

推薦閱讀:

全志的芯片為什么能覆蓋到各行各業?專訪全志科技集團副總裁胡東明