【導讀】構建具有納伏級靈敏度的電壓測量系統會遇到很多設計挑戰。目前最好的運算放大器(比如超低噪聲AD797)可以實現低于1nV/ Hz的噪聲性能(1 kHz),但低頻率噪聲限制了可以實現的噪聲性能為大約50 nV p-p(0.1 Hz至10 Hz頻段內)。過采樣和平均可以降低寬帶噪聲的rms貢獻,但代價是犧牲了更高的數據速率,且功耗較高,但過采樣不會降低噪聲頻譜密度,同時它對1/f區內的噪聲無影響。

此外,為避免來自后級的噪聲貢獻,就需要采用較大的前端增益,從而降低了系統帶寬。如果沒有隔離,那么所有的接地反彈或干擾都會出現在輸出端,并有可能破壞放大器及其輸入信號的低內部噪聲的局面。表現良好的低噪聲儀表放大器可以簡化設計,并降低共模電壓、電源波動和溫度漂移引起的殘留誤差。

低噪聲儀表放大器AD8428提供2000 精確增益,具備解決這些問題所必須的一切特性。AD8428 具有5 ppm/°C最大增益漂移、0.3 μV/°C最大失調電壓漂移、140 dB最小CMRR至60 Hz(120 dB最小值至50 kHz)、130 dB最小PSRR和3.5 MHz帶寬,適合低電平測量系統。最引人注目的是該器件的1.3 nV/ Hz電壓噪聲(1 kHz)和業界最佳的40 nV p-p噪聲(0.1 Hz至10 Hz)性能,在極小信號下具有高信噪比。兩個額外的引腳可讓設計人員改變增益或增加濾波器來降低噪聲帶寬。這些濾波器引腳還提供了降低噪聲的獨特方法。

使用多個AD8428 儀表放大器降低系統噪聲

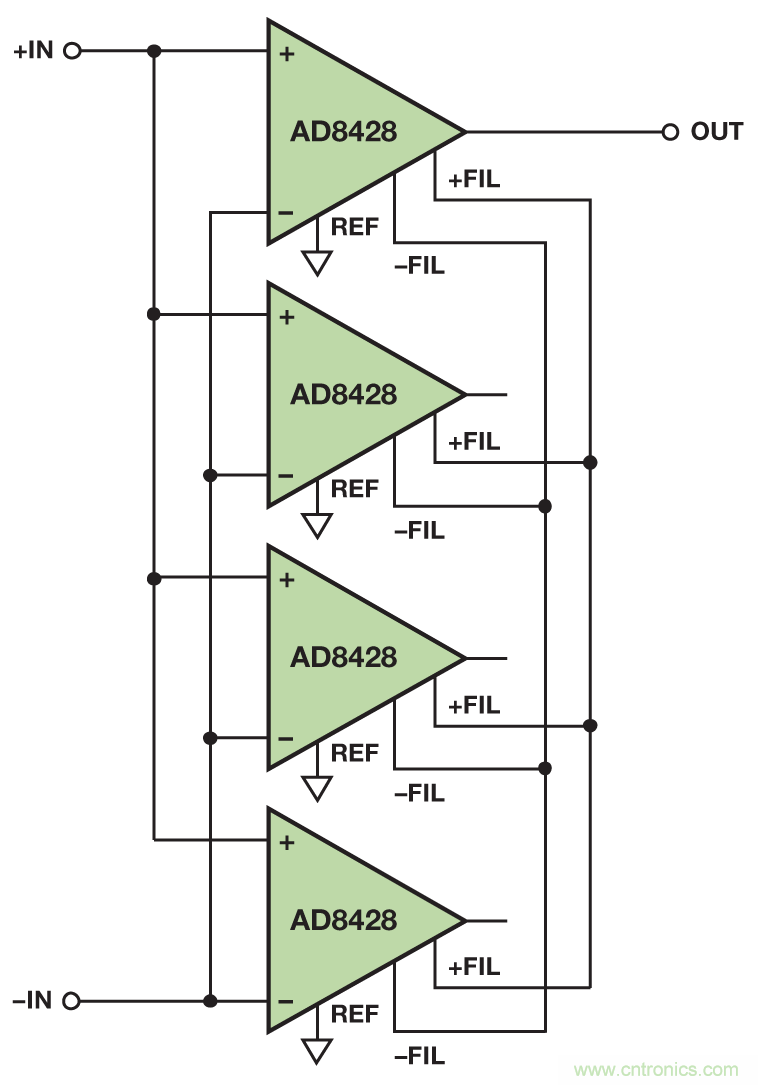

圖1 顯示的電路配置可進一步降低系統噪聲。四個AD8428 的輸入和濾波引腳互相短接,降低噪聲至原來的二分之一。可以使用任意一個儀表放大器的輸出來保持低輸出阻抗。此電路可以擴展從而降低噪聲,降低的倍數為所用放大器數的平方根。

圖1. 使用四個AD8428 儀表放大器的降噪電路

電路如何降低噪聲

每一個AD8428 產生1.3 nV/ Hz折合到輸入(RTI)的典型頻譜噪聲,該噪聲與其他放大器產生的噪聲不相關。不相關的噪聲源以方和根(RSS)的方式疊加到濾波器引腳。另一方面,輸入信號為正相關。每一個AD8428 都響應信號在濾波器引腳上生成相同的電壓,因此連接多個AD8428 不會改變電壓,增益保持為2000。

噪聲分析

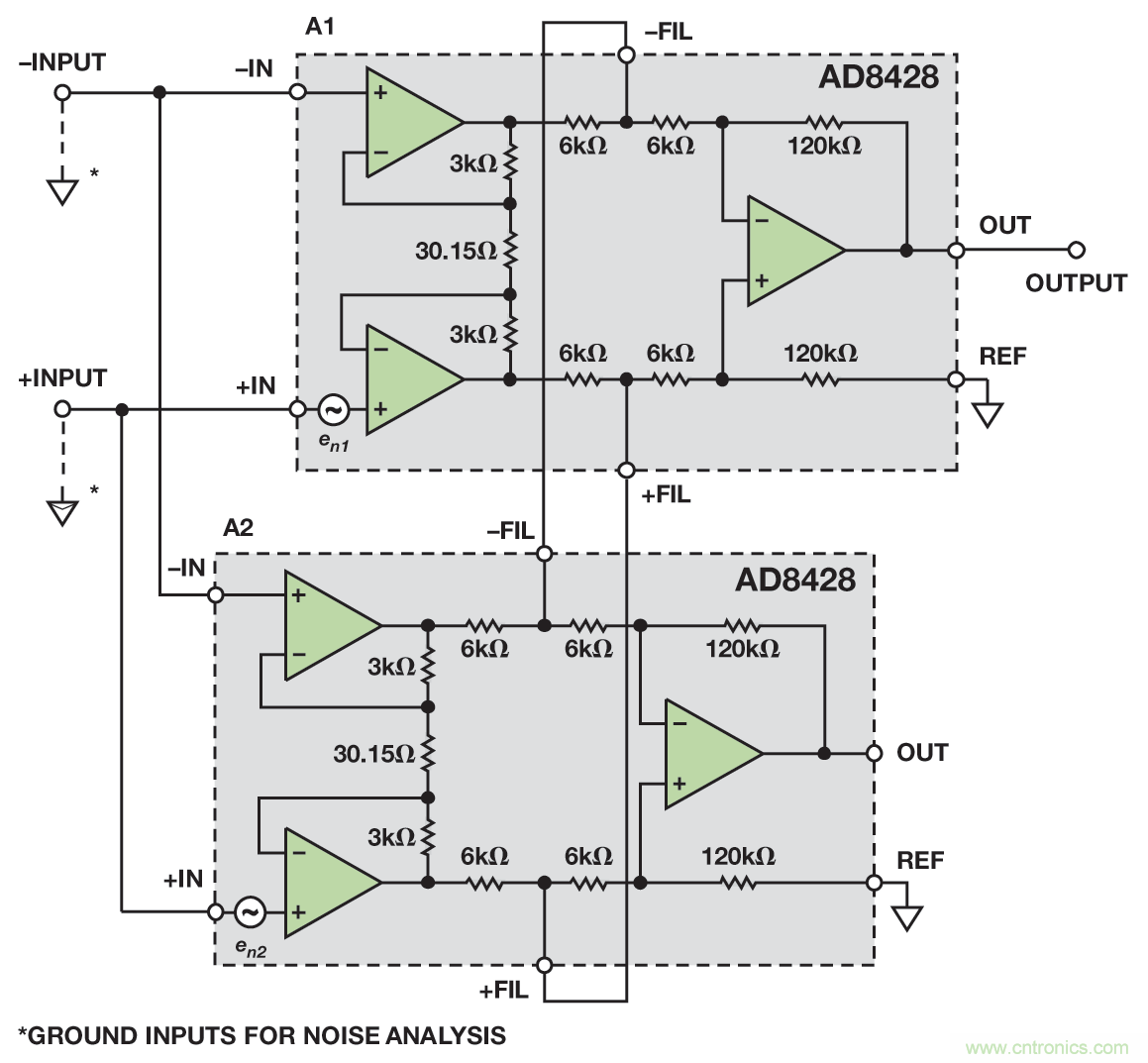

針對圖2電路簡化版本的分析表明,將兩個AD8428以此方式連接可以降低噪聲,降低的倍數為2。每一個AD8428的噪聲都可以在+IN引腳上建模。為了確定總噪聲,可以將輸入接地,并使用疊加來組合噪聲源。

噪聲源en1經200差分增益放大,并到達前置放大器A1的輸出端。就這部分的分析而言,輸入接地時,前置放大器A2的輸出端無噪聲。前置放大器A1每個輸出端與相應前置放大器A2輸出端之間的6 kΩ/6 kΩ電阻分頻器可以采用戴維寧等效電路替代:前置放大器A1輸出端噪聲電壓的一半以及一個3 kΩ串聯電阻。這部分就是降低噪聲的機制。完整的節點分析表明,響應en1的輸出電壓為1000 × en1。由于對稱,因此響應噪聲電壓en2的輸出電壓為1000 × en2。en1和en2幅度都等于en,并且將作為RSS疊加,導致總輸出噪聲為1414 × en。

圖2. 噪聲分析簡化電路模型

為了將其折合回輸入端,就必須驗證增益。假設在+INPUT和–INPUT之間施加差分信號VIN。A1第一級輸出端的差分電壓等于VIN × 200。同樣的電壓出現在前置放大器A2的輸出端,因此沒有分頻信號進入6 kΩ/6 kΩ分頻器,并且節點分析表明輸出為VIN × 2000。因此,總電壓噪聲RTI為en × 1414/2000,等效于en/2。使用AD8428的1.3 nV/Hz典型噪聲密度,則兩個放大器配置所產生的噪聲密度約為0.92 nV/Hz。

使用額外的放大器之后,濾波器引腳處的阻抗發生改變,進一步降低噪聲。例如,如圖1所示使用四個AD8428,則前置放大器輸出端到濾波器引腳之間的6 kΩ電阻后接三個6 kΩ電阻,分別連接每一個無噪聲前置放大器的輸出端。這樣便有效地創建了6 kΩ/2 kΩ電阻分頻器,將噪聲進行四分頻處理。因此,正如預測的那樣,四個放大器的總噪聲便等于en/2。

進行噪聲與功耗的權衡取舍

主要的權衡取舍來自功耗與噪聲。AD8428具有極高的噪聲-功耗效率,輸入噪聲密度為1.3 nV/Hz(6.8 mA最大電源電流)。為了進行對比,考慮低噪聲AD797運算放大器——該器件需要10.5 mA最大電源電流來達到0.9 nV/Hz。一個分立式G = 2000低噪聲儀表放大器采用兩個AD797運算放大器和一個低功耗差動放大器構建,需要使用21 mA以上電流,實現兩個運算放大器和一個30.15 Ω電阻貢獻的1.45 nV/Hz噪聲RTI性能。

除了很多放大器并聯連接使用的電源考慮因素外,設計人員還必須考慮熱環境。采用±5 V電源的單個AD8428因內部功耗會使溫度上升約8°C。如果很多個器件靠近放置,或者放置在封閉空間,則它們之間會互相傳導熱量,需考慮使用熱管理技術。

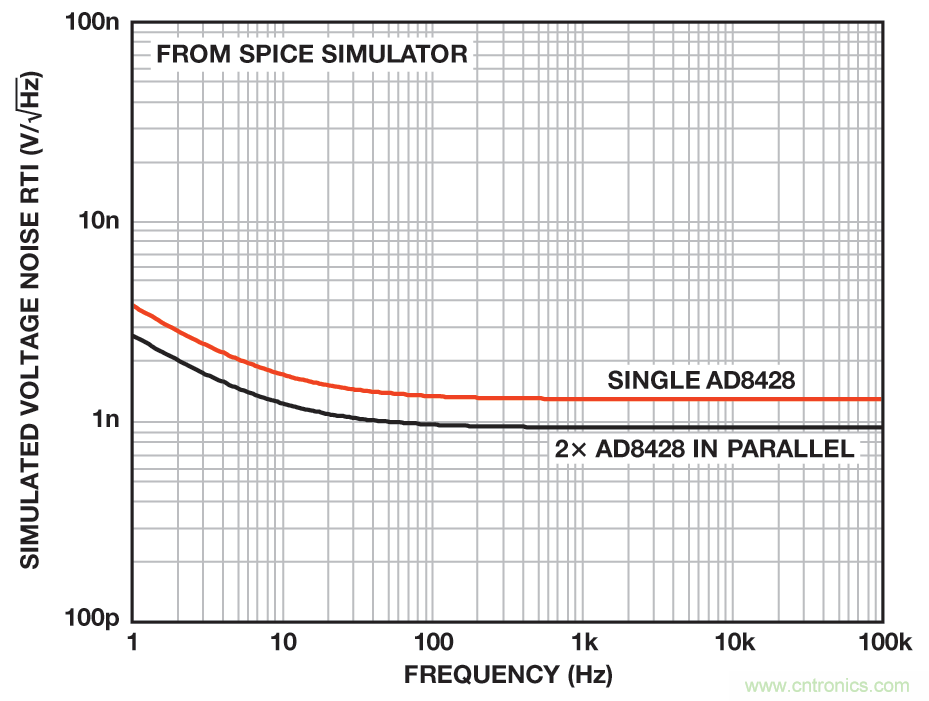

SPICE仿真

SPICE電路仿真雖然不能代替原型制作,但作為驗證此類電路構想的第一步很有用。若要驗證此電路,可以使用ADIsimPE仿真器和AD8428 SPICE宏模型仿真兩個器件并聯時的電路性能。圖3中的仿真結果表明該電路的表現與預期一致:增益為2000,噪聲降低30%。

圖3. SPICE仿真結果

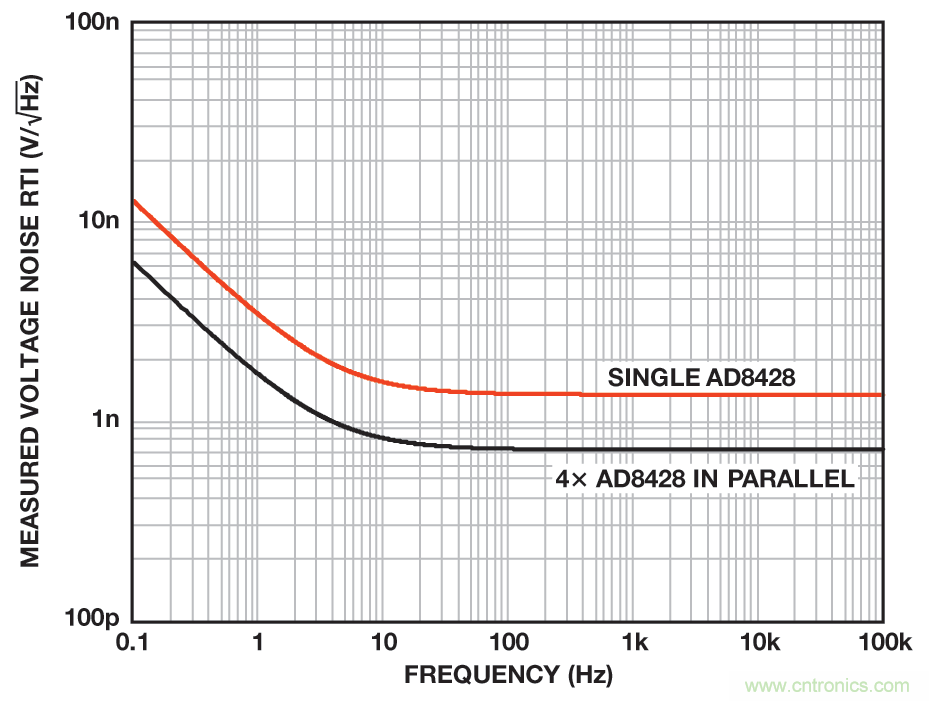

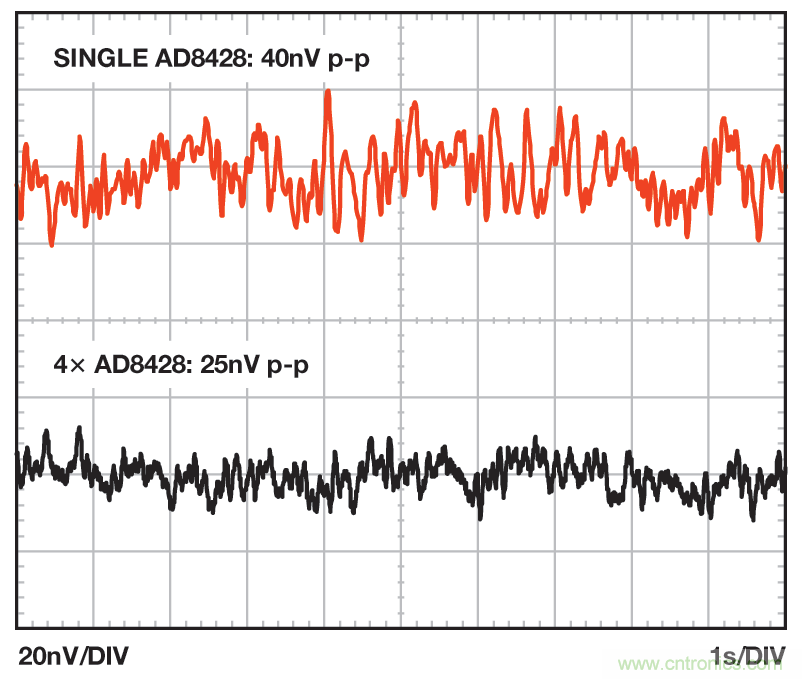

測量結果

在工作臺上測量四個AD8428組成的完整電路。測得的RTI噪聲頻譜密度為0.7 nV/Hz (1 kHz),0.1 Hz至10 Hz范圍內具有25 nV p-p。這比很多納伏電壓表的噪聲都要更低。測得的噪聲頻譜和峰峰值噪聲分別如圖4和圖5所示。

圖4. 圖1中電路的電壓噪聲頻譜測量值

圖5. 圖1中電路測得的0.1 Hz至10 Hz RTI噪聲

結論

納伏級靈敏度目標非常難以達成,會遇到很多設計挑戰。對于需要低噪聲和高增益的系統,AD8428儀表放大器具有實現高性能設計所需的特性。此外,該器件獨特的配置允許將這個不尋常的電路加入其納伏級工具箱內。

參考電路

MT-047指南:運算放大器噪聲。

MT-048指南:運算放大器噪聲關系:1/f噪聲、均方根(RMS)噪聲與等效噪聲帶寬。

MT-049指南:單極點系統的運算放大器總輸出噪聲計算。

MT-050指南:二階系統的運算放大器總輸出噪聲計算。

MT-065指南:儀表放大器噪聲。

推薦閱讀: